本文来自微信公众号:果壳硬科技(ID:guokr233),作者:付斌,编辑:李拓,原文标题:《1nm军备竞赛背后,是芯片厂商的文字游戏》,题图来自:视觉中国

现在,从CPU到GPU,都会听到10nm、7nm、5nm这样的字眼,通过这一参考数字便可轻松直观地悉知工艺进步情况,消费者也普遍会利用这一数字选择产品。

但就这样一个简单的数字背后,却存在着一些“猫腻”,一些厂商利用它背后的漏洞,玩起了文字游戏。

有钱人的游戏

纳米究竟是怎样的概念?1nm相当于万分之一的头发粗细,形象地讲,1nm的物体放到乒乓球上,就像一个乒乓球放在地球上一般[1]。而硅原子的直径为0.117nm,5nm意味着只有约43颗原子的大小,3nm只有约26颗原子的大小。芯片从业者就是行走在微观世界的雕刻家。

此处厂商用到的纳米数字是区分芯片工艺而使用的一种数字,也被称为制程。制程直接影响芯片组的性能优劣、电源效率和体积[2],它一般以28nm为分水岭,区分先进制程和成熟制程[3],前者多用于对计算性能要求更高的领域,后者用于成本较高的场景。虽然两种制程都很重要,但更先进的制程代表的是厂商的硬实力。[4]

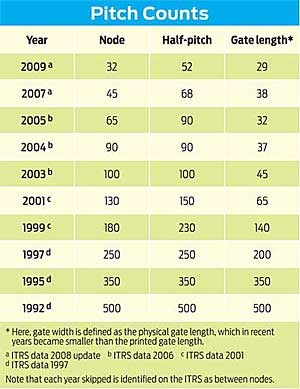

这串数字是如何得来的?制程最早以前指代的是晶体管的物理特征,包括栅极长度和晶体管半截距(half-pitch),栅极长度用于测量二维晶体管晶体管源极和漏极的间距,晶体管半截距是指芯片内部互联线间距离的一半,即光刻间距的一半。

![不同晶体管结构示意图,图源丨泛林半导体<sup>[5]</sup><br>](https://i.aiapi.me/h/2022/03/15/Mar_15_2022_23_58_06_34387257270771077.png)

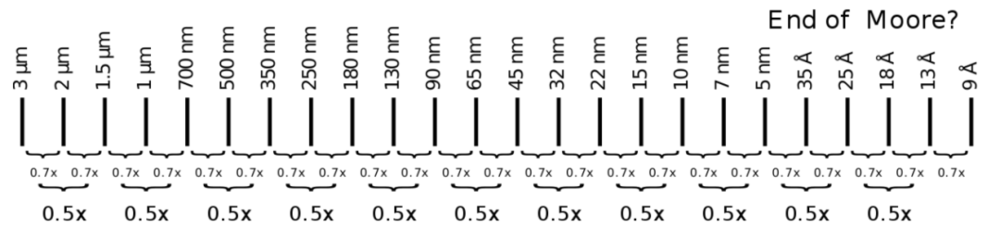

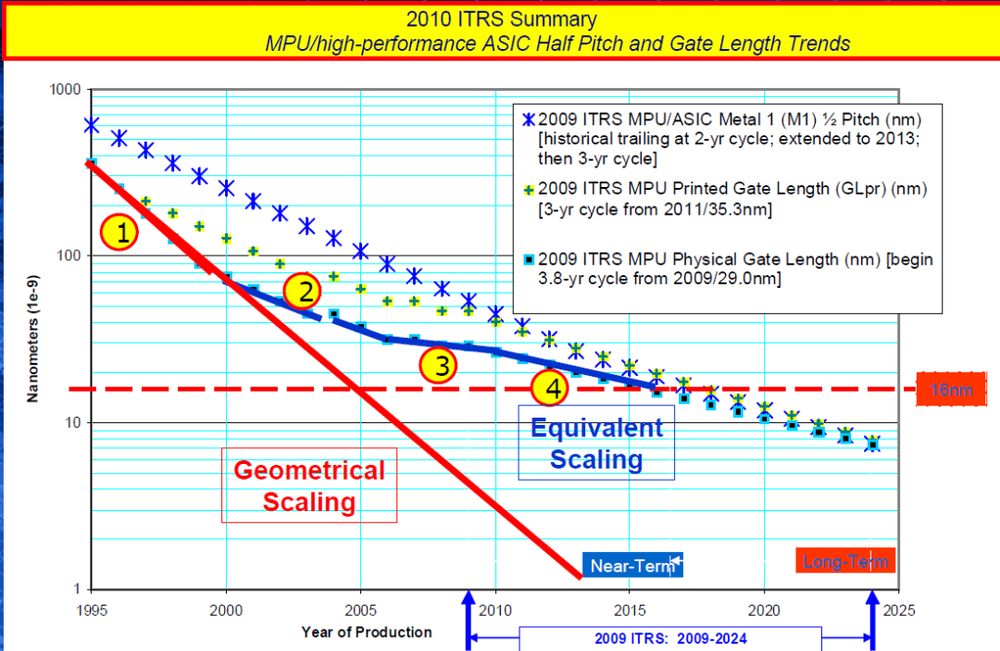

而制程的演进实际上是摩尔定律自我驱动下的预言结果,为实现摩尔定律中对于芯片每隔18~24个月增加一倍晶体管容纳量的定义[6],栅极长度和晶体管半截距在每个节点上都需要增长约0.7倍[7],由此计算出的结果进行排布便是最原始的制程节点。

虽然提升制程有很多好处,但它对厂商来说是昂贵的游戏。据DIGITIMES估计,建设一座28nm晶圆厂投资额达60亿美元,到5nm晶圆厂投资额高达160亿美元[8]。另据IBS数据,3nm芯片设计费用达5亿~15亿美元,兴建一条3nm产线成本为150亿~200亿美元[9]。目前,舞台上只剩下台积电(TSMC)、三星(Samsung)、英特尔(Intel)三个玩家角逐最顶尖的先进制程。

谁在玩文字游戏

时间回到2014年,英特尔还是制程霸主,在当年率先迈入14nm制程。时隔一年,三星和台积电才各自推出14nm和16nm制程,但万万没想到的是这却成了英特尔最后的辉煌。

2017年,三星和台积电相继宣布10nm制程进入量产阶段,但此时英特尔却只能在14nm之后加个“+”号,从数字上来看,英特尔这次输掉了先手优势。

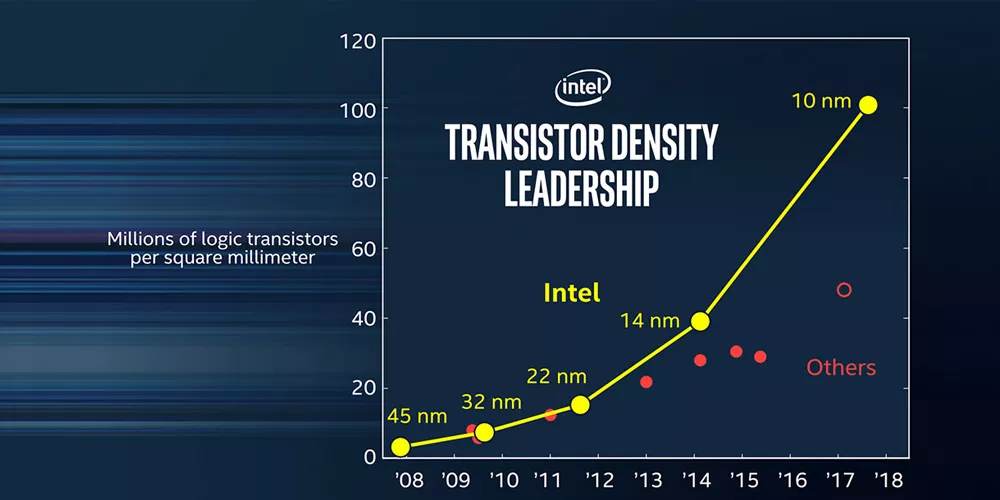

在竞争首次失利后,2017年3月,时任高级研究员、流程架构和集成总监Mark Bohr 在英特尔官网上指出,行业需要一个全新的制程度量方法,以便创造公平的竞争环境,让客户能够轻松比较不同的芯片工艺。

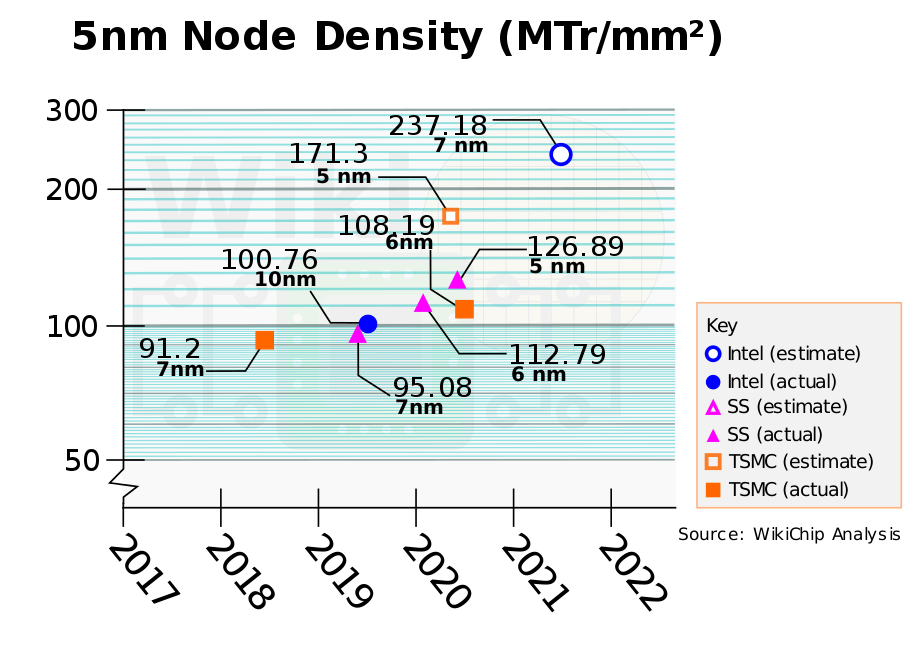

他提出可以利用标准化的密度指标当作全新的制程衡量方式,同时还放出一张不同制程节点下晶体密度的规划图,图中显示其他厂商早已偏离制程应在的落点[10]。换言之,其他厂商根本是在玩文字游戏。而彼时这张图也似乎在宣誓,英特尔的10nm在2018将会面世。

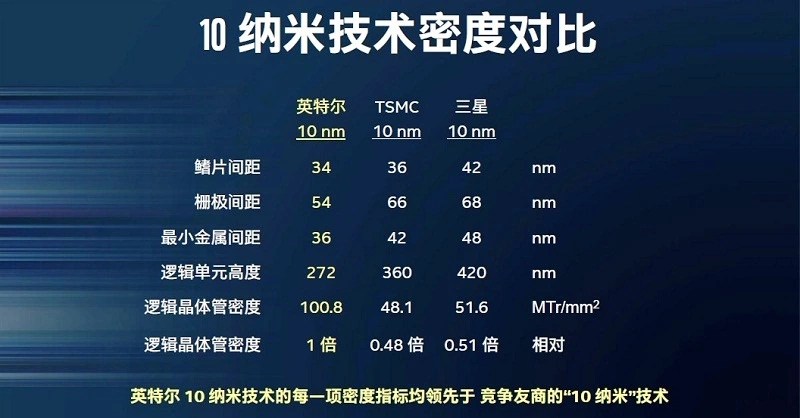

紧接着,在2017年9月,英特尔召开发布会推出自家的10nm制程,少有地将台积电和三星并列对比,在问及为何直指友商时,英特尔说道:“老虎不发威,当我是病猫吗?”[11]

但此后,英特尔的10nm却再也没了消息,10nm成了英特尔过不去的坎。最后回过头来,发现在14nm节点兜兜转转了很多年,只搞出14nm+和14nm++,落了个“牙膏厂”的外号[12]。而到2019年,英特尔终于量产10nm了,世界却变了天,三星和台积电的制程已到达7nm/6nm,5nm蓄势待发。

实际上,对于纳米数字这个称谓,英特尔是保守的。据EETimes China分析,三星在制程命名上是冒进的,假若以三星的标准来看,英特尔的14nm+++(英特尔早期规划中的制程,未正式发布)完全可以命名为12nm,甚至是10nm。[13]

在HotChips31(2019年)上,台积电研究副总裁Philip Wong表示,现在多少纳米代表的只是技术上的迭代,就像车型号一样不具明确意义,所以请不要将节点与实际提供技术的名称混淆。[14]

时隔一年,台积电营销负责人Godfrey Cheng也承认,从0.35μm(350nm)开始,纳米数字就不再真正代表物理尺度了,只是一种行业标准化术语。他与Mark Bohr的观点一致,认为工艺节点需要一种全新的描述化语言。[15]

没有参与到文字游戏中的英特尔,在2021年7月正式“反击”,引入全新的命名体系,将原本的10nm Enhanced SuperFin更名为Intel 7,将7nm更名为Intel 4,之后继续延续这种命名方式分别称为Intel 3、Intel 20Å、Intel 18Å(Å即埃米,1纳米=10埃米)。[16]

这一次,英特尔也加入了文字游戏的行列,甚至还创造一种埃米级的命名方式。另外,按照摩尔定律计算下,的确会出现1.8nm、1.3nm、0.9nm之类的数字,埃米还能避免小数点的出现,一举两得。

资料来源丨国海证券研究所、远川互联网组、各公司官网

偏离的曲线

为什么说三星和台积电是在玩文字游戏?

实际上,一开始栅极长度和晶体管半截距是相等的,且与纳米数字相对应[17]。但从1997年开始,基于纳米数字的传统制程节点命名方法已不再与晶体管实际的栅极长度相对应,并且在14nm以后,这些数字就几乎不存在任何物理上的意义了,仅仅相当于一个代号[18]。假若几何缩放真的能够与实际特征大小同步,那么2015年,业界就会进入1nm制造时代。[19]

以2011年为例,英特尔在22nm节点上切换为FinFET结构,其栅极长度为26nm,半间距为40nm,鳍片则为8nm。[20]

继续沿用没有物理意义的纳米数字的方式其实是有迷惑性的,一方面,会让人认为是物理几何上的微缩,另一方面,会让人误解半导体技术已经达到物理极限。[21]

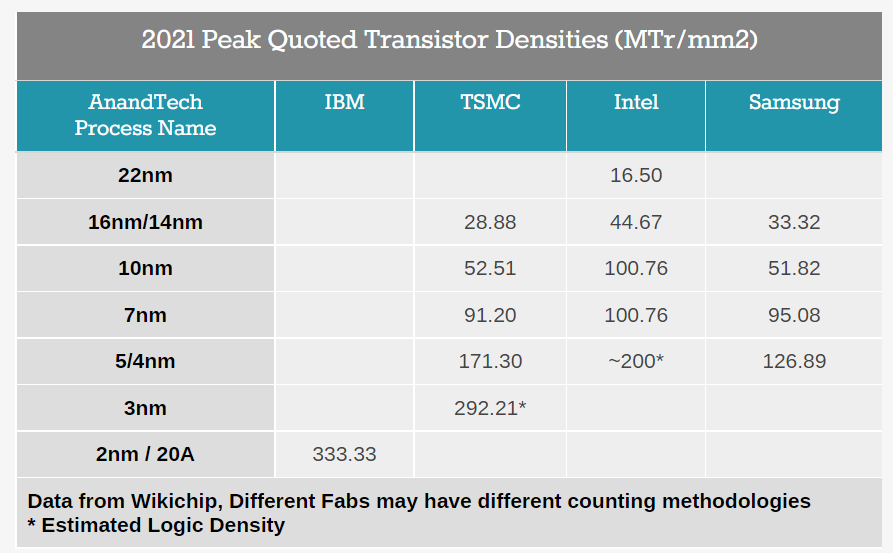

通过对比发现,同一代制程的晶体管密度英特尔将近是台积电的一倍。当英特尔将其10nm更名为Intel 7时,晶体管密度仍然是与台积电7nm相当的。[22]

对台积电来说,性能较上一代有提升,这一数字也与物理毫不相关,即便不在正确的摩尔定律对应点上,这样叫也没什么问题。

业内人士指出,将英特尔的制程转换为“等效节点”(EN),预计英特尔原规划的7nm的EN值为4.1nm,介于三星、台积电的5nm和3nm之间;英特尔原规划的5nm的EN值为2.4nm,介于三星、台积电的3nm和2nm之间。[23]

Tom's Hardware指出,对于不了解内情的人,英特尔的10nm Superfin架构听起来远不如AMD使用的台积电7nm,这是具有欺骗性的。[24]

不过仍然需要指出的是,英特尔的10nm的确晚了一些,现在三星和台积电的晶体管密度早已赶超英特尔,落后和挤牙膏是不争的事实,甚至英特尔现任CEO帕特·基辛格也承认了这种落后,所以现在英特尔将希望都押注在了Intel 20Å,即原2nm上。[25]

新的游戏规则

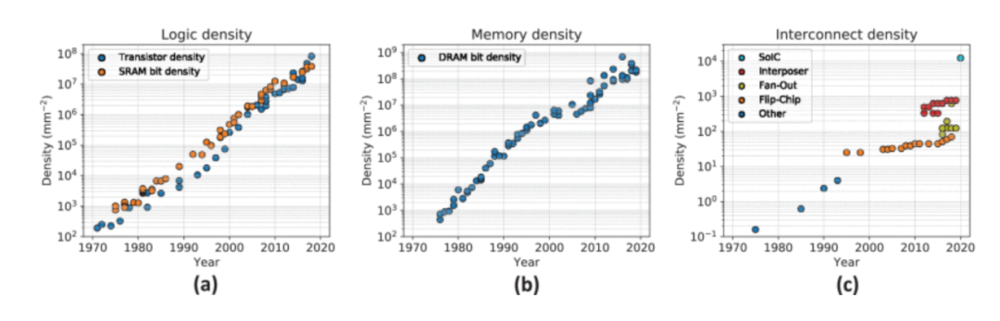

既然利用纳米数字衡量制程误导性那么强,有什么更优解吗?IEEE一篇文章中建议采用LMC密度指标度量半导体基本技术,LMC密度指标分为三个部分:逻辑晶体管密度DL、主存储器密度DM、主存储器与逻辑晶体管间连接密度DC。

虽然业界更偏向用喜欢的标签来推销自己的技术,但LMC密度指标作为一种通用语言,能够更加均衡地衡量半导体制造商之间的技术进步。[26]

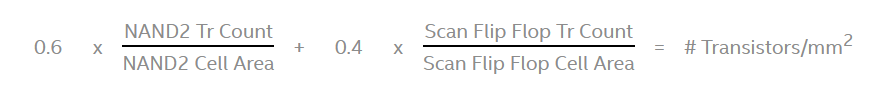

Mark Bohr则是建议对2 bit NAND(4个晶体管)和SFF(Scan Flip Flop,扫描触发器)密度进行综合计算,并建议每个芯片制造商在提到工艺节点时,都以MTr/mm²(百万晶体管每平方毫米)为单位披露“NAND+SFF”的密度指标,同时考虑到工艺不同,最好还可以再单独报告SRAM单元尺寸。[10]

虽然Mark Bohr在之前的提议确有一定道理,但让竞争对手公开晶体管密度并跟着自己规则走,并不是一件能引起行业共识的事情。

反观三星和台积电,利用文字游戏成功逆袭后,又在密度逐渐赶超英特尔,一时间逼迫对手改名是不现实的,所以英特尔才要创造出一种完全不同的符号。

从现在来看,三大厂商都将押注2nm/Intel 20Å,新一轮争霸战即将打响。

References:

[1] 中国科学院兰州化学物理研究所科普网站:“纳米”的概念.2010.2.26.http://www.licp.cas.cn/kxcb/kpwz/201002/t20100226_2784926.html

[2] 联发科官网:https://www.mediatek.cn/innovations/fabrication-process-technology

[3] 半导体行业观察:主流先进制程工艺梳理.2019.9.30.http://www.semiinsights.com/s/electronic_components/23/37805.shtml

[4] 半导体行业观察:台积电与三星的新战场.2020.10.27.https://mp.weixin.qq.com/s/o-Orzda-9cE6N0jcwjsUJw

[5] 泛林半导体设备技术:Nerissa Draeger博士:全包围栅极结构将取代FinFET.2021.1.21.https://mp.weixin.qq.com/s/hmsJMDdxiVStgica4LR2gA

[6] Moore, G.E. ,“Cramming More Components onto Integrated Circuits”. Electronics.1965,38(8): pp.114-117.

[7] WikiChip:Technology Node.https://en.wikichip.org/wiki/technology_node

[8] DIGITIMES:行业观察:昂贵的半导体游戏.2021.12.21.https://www.digitimes.com/news/a20211221VL200.html?mod=3&q=foundry+process

[9] Semiconductor Engineering:Big Trouble At 3nm.2018.8.21.https://semiengineering.com/big-trouble-at-3nm/

[10] Intel:Let’s Clear Up the Node Naming Mess.2017.3.28.https://newsroom.intel.com/editorials/lets-clear-up-node-naming-mess/#gs.st2vcj

[11] EDN China:全球首次亮相10nm工艺,英特尔如何玩转工艺节点的数字游戏.2017.9.21.https://www.ednchina.com/news/20170921intel.html

[12] 新智元:牙膏厂变天!英特尔10nm落后,7nm难产,「蓝色巨人」要靠「代工」谋生?.2021.10.21.https://mp.weixin.qq.com/s/maanJqXs9ENraAxtXIwnCg

[13] EETimes China:Intel 7nm改名为Intel 4背后,用5年重现昔日荣光?.2021.7.29.https://www.eet-china.com/news/202107291014.html

[14] PCGames:TSMC’s 7nm, 5nm, and 3nm “are just numbers… it doesn’t matter what the number is”.2019.9.10.https://www.pcgamesn.com/amd/tsmc-7nm-5nm-and-3nm-are-just-numbers

[15] 快科技:Intel眼中的“假7nm” 台积电:N7制程节点命名遵循惯例、确非物理尺度.2020.2.25.https://news.mydrivers.com/1/674/674272.htm

[16] 知IN:英特尔加速制程工艺和封装技术创新.2021.7.27.https://mp.weixin.qq.com/s/IYlq4bo1Vf_ccFOvAz92WQ

[17] IEEE:A BETTER WAY TO MEASURE PROGRESS IN SEMICONDUCTORS.2020.7.21.https://spectrum.ieee.org/a-better-way-to-measure-progress-in-semiconductors

[18] 面包板:7nm究竟是指晶体管的哪部分?14nm是7nm的四倍?.2020.7.13.https://mbb.eet-china.com/blog/3893689-416167.html

[19] ExtremeTech:How Are Process Nodes Defined?. 2021.2.12.https://www.extremetech.com/computing/296154-how-are-process-nodes-defined

[20] 至顶头条:摩尔定律既已失效,我们该用什么方法衡量半导体进步?.2020.7.24.https://mp.weixin.qq.com/s/GC72EZdlPV9KxJd5F9AD7A

[21] T. N. Theis and H.-S. P. Wong, "The end of Moore’s law: A new beginning for information technology", Comput. Sci. Eng., vol. 19, no. 2, pp. 41-50, Mar. 2017.

[22] EEjournal:No More Nanometers It’s Time for New Node Naming.2020.7.23.https://www.eejournal.com/article/no-more-nanometers/

[23] 知IN:媒体观点 | 技术派灵魂人物回归英特尔:背后实际是这样的伪命题.2021.2.22.https://mp.weixin.qq.com/s/QAptv1QY_zKWqDrXYaKMPA

[24] Tom's Hardware:Forget 10nm? Intel May Change CPU Naming Scheme.2021.4.1.https://www.tomshardware.com/news/intel-new-node-shrink-measurement

[25] AI前线:英特尔:再给我五年,重回巅峰!.2021.7.27.https://mp.weixin.qq.com/s/ahizgqgVoNfrOy-_w04xjg

[26] H. . -S. P. Wong et al., "A Density Metric for Semiconductor Technology [Point of View]," in Proceedings of the IEEE, vol. 108, no. 4, pp. 478-482, April 2020, doi: 10.1109/JPROC.2020.2981715.

本文来自微信公众号:果壳硬科技(ID:guokr233),作者:付斌,编辑:李拓