本文来自微信公众号:爱范儿 (ID:ifanr),作者:杜沅傧,原文标题:《苹果都嫌贵,因为成本太高,台积电放弃 N3 工艺》,题图来自:视觉中国

出道即巅峰,几乎就是苹果 M 芯片的真实写照。

以往来说,MacBook 主打的是优雅设计和 macOS 生态优势,而开始转向 M 芯片之后,MacBook 最大的特色就逐步变成了自研芯片。

发布会上,对于新款 MacBook,关注重点也从设计、制造工艺和跨平台生态中,逐步转向新芯片有着如何的提升。

不过,在 M1 系列的高光之下,今年的 M2 芯片却黯淡了许多。

这其中可能是由于期待值过高带来的反差,但主要的原因还是在于采用了与 M1 相同的台积电 5nm 工艺制程。

纵使苹果坐拥 Arm 芯片最强设计团队,也无法摆脱物理限制。

在 M2 内采用了与 A15 中类似的 Avalanche 性能核心和 Blizzard 能效核心,且 M2 增加了核心数、芯片面积和总晶体管数。

一通操作下来,M2 相对于 M1 有着 18% CPU 和 35% GPU 的性能提升。

从数字上来看,似乎算是升级较为明显的迭代,只是在实际之中,搭载 M2 的产品却出现了许多问题(SSD 降速、降频、核心过热),不如同期的 M1 产品。

其实在 M2 发布之前,就传出台积电正在努力试产第一代 3nm 工艺芯片,苹果也将会是第一批客户。

随着 5nm M2 的落地,DigiTimes 就报道苹果已经包下台积电 3nm 芯片所有的产能,不仅是为了 M3 芯片,也会用于 M2 Pro、M2 Max 芯片的生产。

如此来说,在 3nm 工艺之下,M2 Pro、M2 Max 将会有着明显的能效提升,远超 M2 芯片。在一代芯片内采用不同的工艺,在业内也实属罕见。

成本太高,没人下单,台积电放弃 N3 工艺制程

对于 3nm 芯片,不光是苹果,Intel、AMD、英伟达都在排队等台积电 3nm 产能,供不应求。

而台积电也如期试产出 3nm 芯片,并达到相应的投产良率。只不过,近日有消息人士称,台积电内部已经决定放弃 N3 工艺。

从积极投产到放弃的 180° 大转弯,根本原因其实也挺简单,就是生产成本太高,高到苹果都不愿意用。

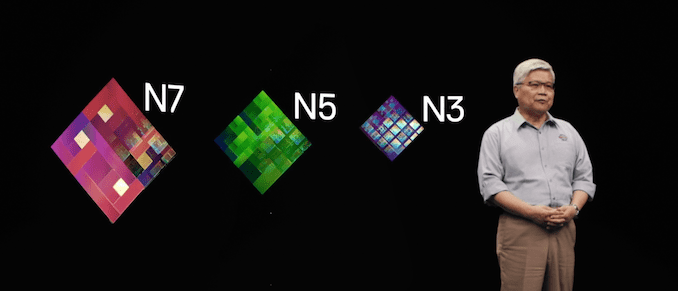

而且,台积电 N3 工艺相对于 N5 工艺,性能有着 10%~15% 的提升,功耗降低 25%~30%,与过高的投入有些不相称。

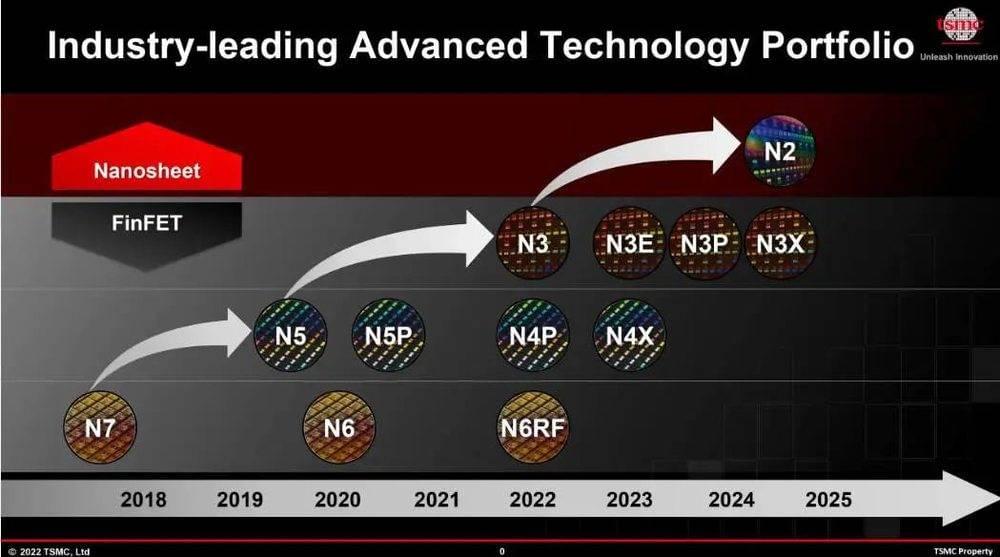

按照台积电的规划,3nm 节点共有 N3、N3E、N3P、N3X 四种工艺,可以理解为 3nm 节点内有四代制造工艺,逐代的性能、晶体管数和成熟度都有着提升。

在放弃 N3,也就是第一代 3nm 工艺后,台积电也开始着手准备更具性价比和成熟度的 N3E 二代工艺。

能效比相对于 N5 工艺来说有着更明显的提升,只不过量产时间可能延后至 2023 年下半年。

这也意味着,原本计划在今年发布的 M2 Pro 和 M2 Max 芯片依然会采用与 M2 相同的 5nm 工艺。

再加上不变的 MacBook Pro 设计,其升级迭代策略就十分像英特尔此前的钟摆(Tick-Tock)升级理论。

三星自认在 3nm 上占据先机

在高端芯片代工上,能与台积电直接竞争的目前也只有三星了。在即将到来的 3nm 工艺节点争夺上,三星一方面战略性放弃 5nm,另一方面便斥巨资建厂建产线堆产能。

并在 7 月份,对外宣布三星半导体已经完成 3nm 芯片的量产和出货。

只不过,三星近两年在芯片代工上频频翻车,曾经的大客户高通、AMD、英伟达都已把新订单交由台积电,似乎并没有其他拥有足够财力的客户来定制 3nm 芯片。

外媒在查询出货名单时,只查到了一家名为上海磐矽的半导体公司,该公司主营业务为虚拟货币挖矿机芯片设计,规模有限。

加上现在虚拟货币市场不景气,很难说三星获得了多少订单。

另一方面,曾经的老客户高通在获知三星 3nm 投产之后,并未着急投片,而是采取了观望的态度。

出货量并不多,也被外界猜测三星这次的 3nm 芯片量产更像是一个“营销手段”,也不排除用的是试产芯片充当量产。

接连失去大客户的三星半导体,目前也仅剩 Exynos 芯片部门一个大客户。只是近来 Exynos 芯片纵使拉上了 AMD 仍然出师不利,也放出消息暂缓 3nm 芯片的投片,最快也要等到 2024 年第二代 3nm 工艺量产之后。

除了 Exynos 芯片部门,Google 的 Tensor 自研芯片也继续交由三星半导体代工,预计在 Tenor 3 上采用三星 3nm 工艺,时间定在 2023 年下半年,与台积电 N3E 量产时间相差不大。

不过,Google 的 Pixel 系列并非是智能手机市场的出货大户,去年年底仅占去了 3% 的全球份额,与高通相差甚远。

按照三星的说法,在 3nm 量产上的确占得了先机,但在后续代工芯片的出货量上,仍然不够明朗。

嗅到了一股移动芯片的牙膏味

对于当下的高端移动芯片来说,先进的工艺制程已经成为它们能效增长的一大因素。

原本预计今年年底量产出货的 3nm 芯片,由于成本过高而延后,可能会引起高端移动芯片的增长瓶颈。

4nm、5nm 依然是近年来高端芯片的主流制造工艺,其能效比可能无法达到此前革新换代而带来的大跨步。

而后续即便按照原计划 2023 年底量产 3nm,成本考量上也很难回到此前的状态。

台积电总裁魏哲家在科技座谈会上表示:“高端、全球化供应系统时代已经过去。”由于许多国家都在争相在国内建厂,后续的生产成本也会水涨船高,“包括通货膨胀,芯片成本正在迅速上升。”

台积电的第一代 3nm 芯片成本居高不下,或许与此原因有关。

另外,按照台积电的规划,2025 年会试产 N2 工艺,愈发接近于工艺制程的物理极限。

并且随着先进工艺制程的推进,晶体管密度的提升,也带来了积热问题,此时像苹果 M 一样疯狂堆积核心增加芯片面积并非是可行之道。

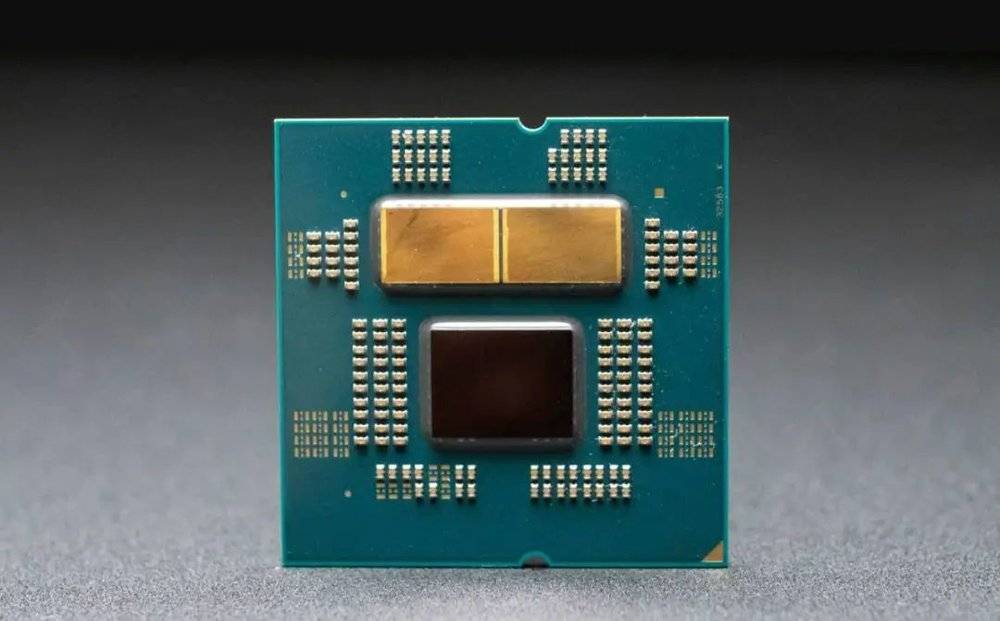

昨天 AMD 如期对外公布了 Zen4 架构,生产工艺从 7nm 升级到 5nm 后,芯片面积缩小 12%,晶体管数却增加了 58%。

相应的锐龙 7000 系处理器,也相较于前代有着较为明显的提升,尤其是在多核表现上。

早在此前的文章中,我也表示 AMD 的 chiplet(小芯片)技术相对来说有着更“光明”的未来,芯片不会完全被代工厂工艺制程所钳制,有着更灵活的升级方式。

而在 3nm 工艺制程量产疑云之下,厂商的芯片设计可能也需要提前布局新的架构,以避免遇到能效瓶颈。

本文来自微信公众号:爱范儿 (ID:ifanr),作者:杜沅傧