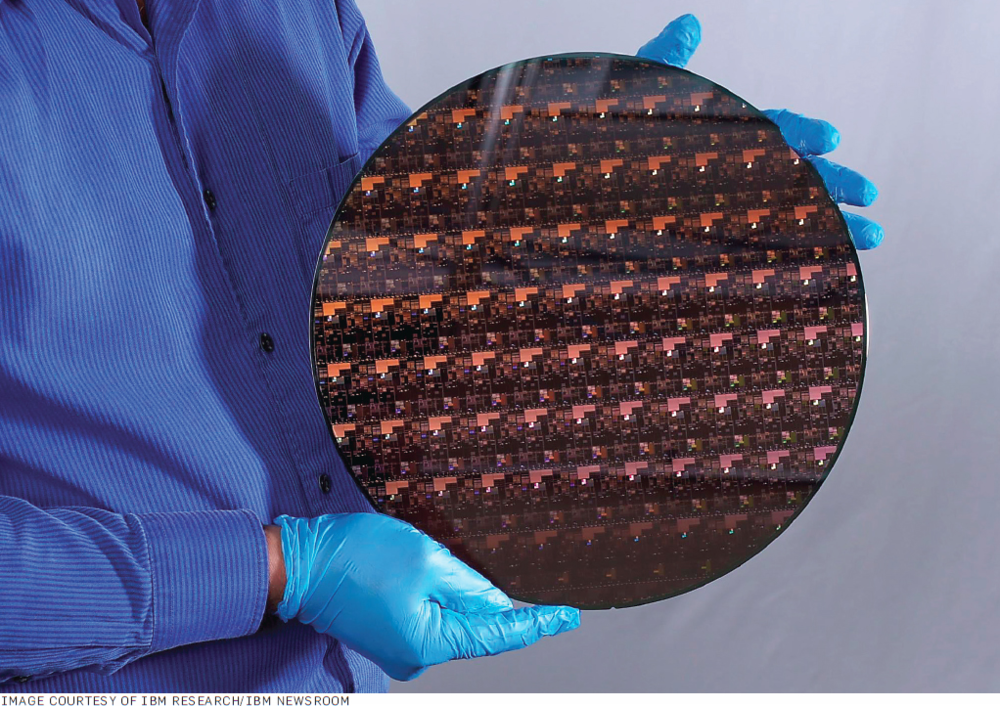

本文来自微信公众号:机器之心(ID:almosthuman2014),作者:Chris Edwards,编译:张倩,原文标题:《3纳米再往下芯片应该怎么造?可能要给半导体加金属了》,头图来自:视觉中国

韩国芯片制造商三星电子计划在 2022 年底投入生产 3 纳米半导体工艺时,率先采用一种新型晶体管,使摩尔定律再延续 10 年。

上次对晶体管结构的重大改变投入生产还是十多年前。FinFET 晶体管出现的时候,平面晶体管结构已经为半导体领域服务了几十年,达到了物理极限。问题在于该晶体管的栅具有相对简单的结构,即在源极和漏极之间薄薄的沟道上放置一个电极,起到静电阀的作用。电压施加在栅上时产生的电场控制电子能否通过通道,决定晶体管是否打开。

本世纪初期,芯片制造商成功地超越了摩尔定律关于栅长的一些预期。65nm 节点的栅长缩短至 30nm,可以快速切换,但漏电(leakage)问题很大。载流子不仅很容易穿过所谓的绝缘栅,从漏极产生的电场线也到达了源极区域。这使得电流在晶体管应该完全关闭时仍在流动。几十年以来,栅长的进一步缩小陷入困境,以至于芯片制造商冒着耗尽空间的风险来放置连接晶体管所需的导电触点。

从 22nm 开始,芯片制造商开始转向 FinFET。与平面晶体管相比,FinFET 器件改进了对沟道的控制,从而减小了短沟道效应。平面晶体管的栅极位于沟道的正上方,而 FinFET 器件的栅极则是三面包围着沟道,能从两边来对沟道进行静电控制。这种设计可以大幅改善电路控制并减少漏电流,也可以大幅缩短晶体管的栅长。

但如今,FinFET 也遇到了与十年前平面晶体管类似的问题:只从三面包围栅极仍然会留下一些沟道漏电的机会。下一步是将沟道完全提升到硅表面之上,这样剩下的一面也能包上。

虽然全环绕栅极晶体管(gate all-around,GAA)有多种可能的结构,但像三星这样的制造商却青睐纳米片(nanosheet)设计,这是 IBM 和法国研究机构 CEA-Leti 15 年前提出的一种结构。它涉及一些颇具挑战性的步骤,但优点是可以重用 FinFET 的许多步骤。这种设计最后得到的不仅仅是一个封闭的沟道,还有若干相互堆叠的沟道:这是一种进一步改进环绕栅极控制的方法。在原来硅鳍的位置,有一个硅和硅 - 锗层组成的三明治结构。硅 - 锗层被用作牺牲层,因为它为化学蚀刻提供了一个容易的目标,化学刻蚀剂会将这些层腐蚀掉。

纳米片的水平波形系数(form factor)提供了一种调整晶体管大小的简单方法。FinFET 的一个主要问题是:在大多数情况下,晶体管中的单个鳍片很少提供足够的电流用于电路,多个鳍片必须并行使用,因此有效宽度以较大的步幅往上增加。三星电子负责设计的副总裁 Taejoong Song 在今年 2 月的国际固态电路会议上表示,他的团队利用了绘制不同宽度的纳米薄片的能力,创造出了比 FinFET 密度更大、更可靠的存储单元。

进一步的提升将以能源效率的形式出现。芯片制造商将利用改进的栅极控制来降低电源电压。由于有功功率消耗与电源电压的平方成正比,所以此处可以节省大量的功耗。

国际器件和系统路线图(IRDS)是一个跟踪半导体技术超过 20 年并为芯片制造商提供指导数据的组织。该组织预计,少数仍能制造顶尖芯片的制造商将在本世纪二十年代中期过渡到纳米薄片结构。但他们的步伐并不一致。

台积电预计,其竞品工艺的首次生产将在今年年底完成,但该公司仍然选择继续使用 FinFET,并表示与之前的 N5 或 5nm 工艺相比,该工艺仍可将密度提高 70%;而纳米薄片工艺将于 2024 年左右在 N2 或 2nm 制程中亮相。

虽然纳米薄片有利于晶体管尺寸的进一步缩小,但它带来的改进远没有过去那么引人注目。IRDS 估计,到 2030 年,12nm 将是硅基晶体管栅长缩小的极限,仅比 3nm 纳米片工艺的可实现尺寸减少 25%。此外,它们能变多窄也是有限制的。然而,IRDS 仍然根据摩尔定律预测,至少到 2030 年,晶体管密度将会翻倍。现在,晶体管的进一步缩小更多地与其布局和连接方式有关,而不是那些设备的尺寸。

对于 IRDS 主席 Paolo Gargini 来说,行业为进一步缩小栅长所做的改变标志着戈登 · 摩尔在 45 年前所说的话仍然有效。“如果你回到 1975 年的演讲,他说,对晶体管尺寸缩小的最大贡献将来自他所谓的‘电路和系统智能’,这是我们在未来十年将做的事情,”Gargini 说。用今天的话来说,摩尔的预言可以被重新表述为“晶体管将进化为灵巧的拓扑 3D 晶体管”。

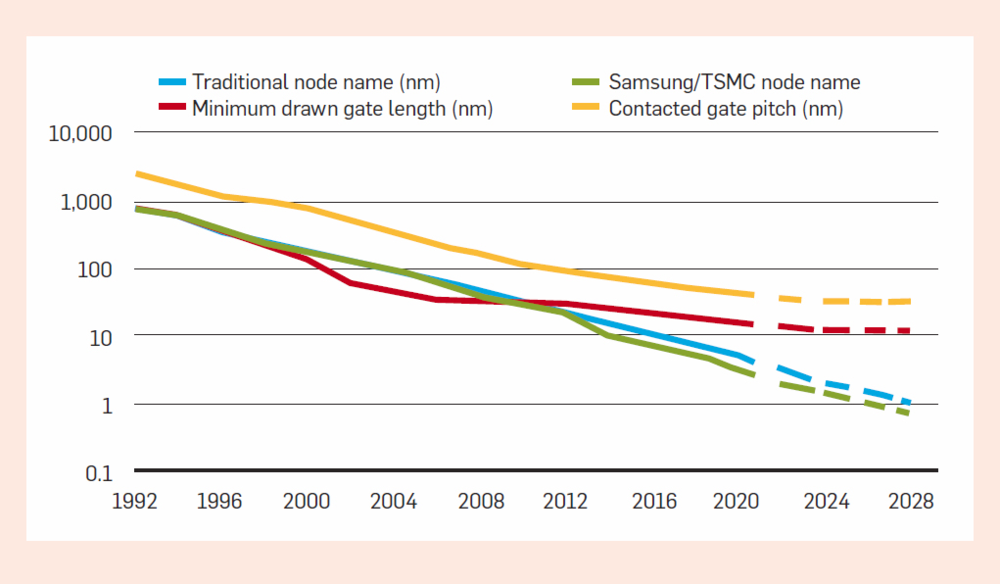

对晶体管布局和连接的强烈关注已经持续了一段时间。这就是为什么进程节点的名称与芯片上的物理维度越发脱节。20 世纪 90 年代,节点名称通常反映金属半节距或栅长。但如今,三星和台积电使用的 3nm 名称已经无法在芯片上找到对应的尺寸。即使英特尔更为保守的 5nm 栅长也与实际栅长有一定的差距,实际栅长至少是英特尔栅长的三倍。

由于很难缩小平行鳍片之间的间距,芯片制造商在过去十年中一直致力于消除其他空间浪费的来源,比如晶体管之间的连接方式。传统上,到栅极的电气连接会被放置在侧面,以避免与源极和漏极连接产生短路的风险。英特尔发现了一种化学方法,可以可靠地将触点直接放置在栅极的顶部,使得在不改变内部尺寸的情况下将晶体管封装得更紧密成为可能。与此同时,芯片制造商努力通过提高平行鳍的高度来减少所需的数量,并设法降低平行鳍在制造过程中崩溃的风险。

当前,业界正设法对核心晶体管周围的电路布局进行更彻底的改变,这进一步增加了制程节点的名称和片上实际结构物理尺寸之间的差距。

几年前,作为 N3 或 3nm 级工艺设计的一部分,比利时研究机构 Imec 提出将电源线路埋在晶体管层下面。如今,这些电源线路对逻辑布线产生了干扰,尤其是因为它们需要个头较大一些,以防高频开关产生的电流脉冲扭曲或破坏它们。

虽然从电路设计师的角度来看,将电源轨埋起来似乎是一个显而易见的选择,但对于芯片制造商来说,这个选择并不容易。Lam Research 子公司 Coventor 的半导体工艺与集成高级经理 Benjamin Vincent 表示,在那个点将金属引入生产流程,“是整个半导体行业几十年来一直在避免的事情”。这种方法所需的高导电性金属很容易污染硅表面,破坏晶体管。

到这个十年结束时,IRDS 委员会希望业界不仅能接受将电源轨埋起来的操作,还能接受一些其他的想法,利用三维空间将晶体管封装在更小的区域内。CEA-Leti 和 Imec 已经推荐了各种堆叠晶体管的方法。其中,Imec 的 CFET(互补场效应晶体管)在所谓的 1.5nm 制程中被寄予厚望,它将两个用于当今大多数逻辑电路的互补晶体管放置在一个垂直堆栈中,从而实现近 50% 的面积压缩。

大规模的垂直集成是有先例的。闪存供应商展示了他们可以垂直堆叠 100 多个存储单元。类似的结构可能会用于逻辑晶体管,尽管这需要另一波制造创新来实现。

Vincent 说:“伴随着堆叠技术的出现,以前水平方向的所有关键尺寸控制要求现在都转向了垂直方向。有了这种垂直 3D 方法,栅的长度将不再由复杂、昂贵的光刻方法控制;相反,它将依赖于薄膜的精确沉积来确定沟道长度。

如果不能克服这些制造方面的挑战,摩尔定律的终结可能要早于预期。然而,IRDS 委员会和芯片制造商们看到,重新强调拓扑“智慧”(topological "cleverness"),而不是概念上更简单的增加面积,是延续摩尔定律的方法,还为 1nm 工艺铺平了道路,即使栅极、导线和芯片上的其他结构是节点名称的 10 倍。

原文链接:

https://cacm.acm.org/magazines/2021/10/255703-a-switch-in-time/fulltext

本文来自微信公众号:机器之心(ID:almosthuman2014),作者:Chris Edwards