本文来自微信公众号:品玩(ID:pinwancool),作者:洪雨晗,原文标题:《先进封装未来将变得和光刻机一样重要?》,题图来自:视觉中国

封装技术从未如此重要过。在今年,先进封装技术已成为了各大晶圆厂、封测厂商甚至一些Fabless的重点投入领域。

9月,联电与封测厂商颀邦相互交换股权;在8月的Hot Chips行业热点大会上,台积电副总经理余振华公布了CoWoS(Chipon Wafer on Substrate)封装技术的路线图,以及先进热处理和COUPE异构集成技术;7月,英特尔公布了未来制程工艺和封装技术路线图,将继续推动Foveros 3D堆叠封装技术与EMIB(嵌入式多管芯互连桥)封装技术的应用;封测龙头日月光则在6月宣布将投入20亿美元用于提高其晶圆封装业务。

半导体产业链上下游厂商已把封装技术提到更加重要的位置,其原因就是先进封装实际上已成为超越摩尔定律的关键赛道。摩尔定律,戈登·摩尔根据自己的经验在半导体领域做的一个预言:“在最小成本的前提下,集成电路所含有的元件数量大约每年便能增加一倍。(The complexity for minimum component costs has increased at a rate of roughly a factor of two per year)

摩尔定律作为半导体迅猛发展的重要推动力,从诞生开始就遭到人们的质疑——是不是再过多少年摩尔定律就要失效了?为此有人还打趣道:“预测摩尔定律要死掉的人数,每两年翻一番。”

如今据摩尔定律的提出已过去了56年,要想在拇指大小的芯片上做出更多的晶体管与更小的制程,变得越来越困难。维持摩尔定律变得越来越困难的原因在于人类遇到了两个难题:一个是成本问题,全球有足够实力尝试7nm及以下制程的芯片制造商也只有台积电、三星、英特尔三家,因为仅仅制造一座先进制程的晶圆厂就需数百亿美元,这还不算日后运营维护和技术研发。

第二个则是技术上的难题,随着芯片尺寸的微缩,短道沟效应导致的漏电、发热和功耗严重问题一直困扰着芯片制程的继续微缩。当材料逼近1nm的物理极限时,量子隧穿效应导致有一定的电子可以跨过势垒,从而漏电,这个问题对于人类来说暂时是无解的,因为物理理论还没有搞清楚这个现象。霍金从物理角度上对其做过一个总结,光的有限速度和材料的原子特性。

虽然摩尔定律到现在仍在艰难维持,但产业界也确实意识到了制程不会无限缩小下去,晶体管也不可能无限增加下去,可要知道的是,摩尔定律首先是一条经济上的定律,然后才是工程科学方面的定律。因为降低特征尺寸能降低芯片制造的整体成本,所以业界才会不断追逐摩尔定律,其背后的逻辑是:半导体行业需要以一个合适的速度增长来降低成本提高利润。

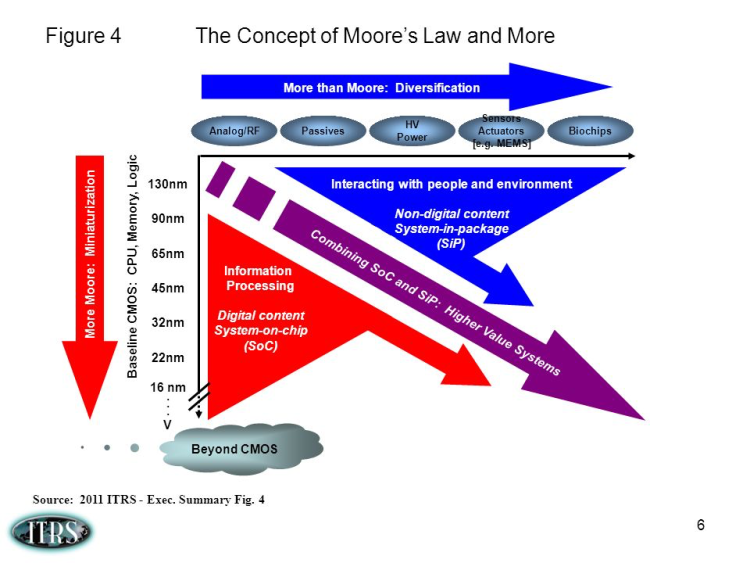

这个时候More than Moore(MTM,超越摩尔定律)——摩尔定律之上的成长动能也因此被广泛提出,产业界试图从更多的途径来维护摩尔定律的发展趋势,而先进封装技术已成为超越摩尔定律的关键赛道。

国内封测技术专家于大全曾表示,无论是延续摩尔定律,还是超越摩尔定律,都离不开先进封装技术,“先进封装将是撬动半导体产业继续向前的重要杠杆。”先进封装到底是什么呢?为何它能作为为摩尔定律续命的关键技术出现?

封装(Package),是把集成电路装配为芯片最终产品的过程,简单地说,就是把铸造厂生产出来的集成电路裸片(Die)放在一块起到承载作用的基板上,把管脚引出来,然后固定包装成为一个整体。它主要要三个作用:通过特殊材料保护脆弱的芯片、将芯片电子功能部分与外界互连以及物理尺度兼容。

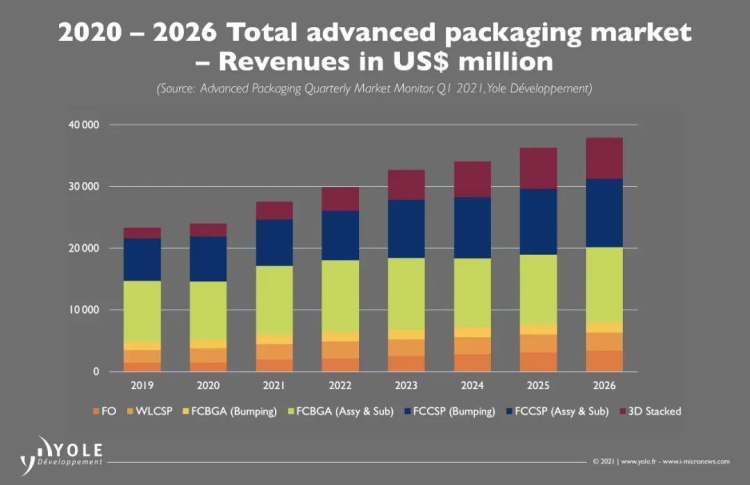

近年来,先进封装市场也确实在迅速发展。据知名分析机构Yole Developpement的预测,先进封装市场预计将在2019-2025年间以6.6%的复合年增长率增长,到2025年将达到420亿美元,远高于对传统封装市场的预期。

先进封装其实是相对传统封装而言的。在业界,先进封装技术与传统封装技术通常以是否焊线来区分。传统的封装技术通常指先将晶圆切割成单个芯片,再进行封装的工艺形式,其包括双排直立式封装DIP与球格阵列封装BGA,需要焊接线路。先进封装则包括倒装(FlipChip)、凸块(Bumping)、晶圆级封装(Waferlevelpackage)、2.5D封装(interposer,RDL等)、3D封装(TSV)等封装技术,其技术并不需要用到线路焊接的方式。

抛开这些复杂的封装术语,产业界将先进封装技术提升到与制程微缩同等重要的原因,在于它能进一步提高芯片的集成度并且降低芯片制造的成本,并且,与继续追逐先进制程不同,它暂时还不涉及到去突破量子隧穿效应等物理极限问题,没有了这些难啃的硬骨头,先进封装技术看起来有良好的发展前景。

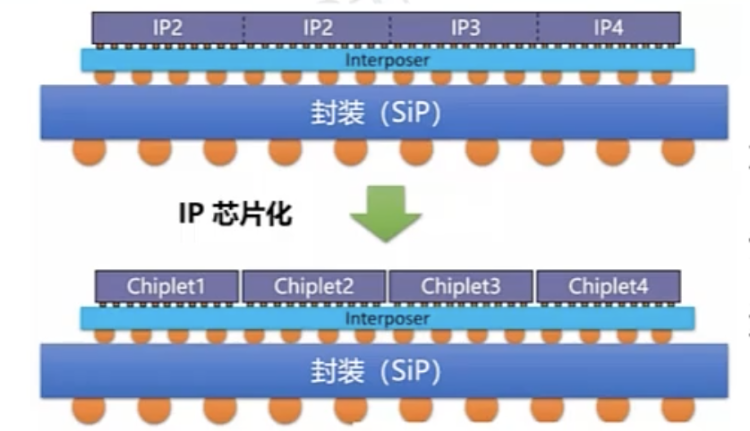

那么先进封装具体是通过怎样的技术原理来实现超越摩尔的呢?这就不得不chiplet技术的发明,chiplet也被称为小芯片,它是系统级芯片(SoC)中IP模块的芯片化,通过chiplet技术可以提高良率和降低成本,同时提高设计的灵活度,缩短设计周期。

简单来说,可以把chiplet技术想象成为一块乐高积木,多个chiplet模块可以拼接成一个系统级芯片(SoC),而在过去,一个系统级芯片(SoC)是不能再次切割的。这样做的好处在于,一块完整的晶圆可以被分成更多的chiplet,这意味着同样良率情况下更低的成本消耗,例如在一片晶圆切割封装时出现了一个点的损伤部位,直接做成一个系统级芯片(SoC)能切成10块,假如做成chiplet是100块,那么这块晶圆做成系统级芯片(SoC)的良品率为90%,而做成chiplet的良品率可以达到99%。

chiplet技术也为异质异构的芯片制造提供了可能,这种模块化的小芯片可以实现不同架构、不同材质、不同工艺节点甚至不同代工厂生产的产品集成到一块芯片上,由此快速产生出一个适应不同功能需求的超级芯片。

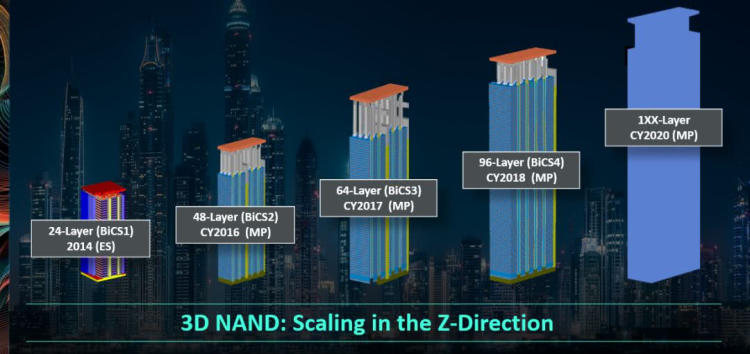

除了chiplet技术以外,3D晶圆级封装也是近年来产业界先进封装技术的发展方向。3D晶圆级封装是指在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,相较于传统的2D电路的平面集成方式,它的集成度要更高,同等空间内可以集成更多芯片。当3D晶圆级封装与chiplet技术相结合,还可以实现不同IP之间的3D堆叠,从而大大降低了封装成本以及能耗。

如今,台积电、英特尔、AMD、日月光等主要芯片设计、制造、封装厂商都逐渐在其产品中应用到了上述先进封装技术,先进封装所扮演的角色无疑是愈加重要了。

对国内的芯片企业而言,先进封装或许是现下适合长期投入的优质赛道,毕竟短期内国内企业还无法通过自研或是进口来获取EUV光刻机。虽然,现在我们处于光刻来驱动尺寸微缩的时代,但未来驱动芯片行业继续往前走的可能是设计与工艺协同优化,以及系统与工艺协同优化的阶段。那么,先进封装或是下一次芯片产业洗牌的开端,中国的自主高端芯片的机会也必蕴含其中。

本文来自微信公众号:品玩(ID:pinwancool),作者:洪雨晗