2023年9月13日,苹果的秋季新品发布会上,与iPhone 15 Pro系列一同登场的,还有全球首款3nm芯片A17 Pro,其依旧出自苹果的老朋友台积电之手。

在这款芯片发布前,大家都对它寄予了厚望,与4nm这样的小节点相比,3nm是继5nm后又一次重要的工艺迭代,回顾过往历史,每次工艺的大升级,都会带来芯片性能的又一次大幅度提升,而3nm本该也是如此。

图片来自:Apple

但意外偏偏发生了,这颗本应强大的A17 Pro芯片提升幅度并没有大家想象中那么大,反而iPhone 15 Pro的发热问题,让苹果变成了“火龙果”。

那么,发热发烫这个锅,是不是要让台积电来背呢?

神仙难救的散热

很快就有人为台积电撑腰了,天风国际分析师郭明錤今日发文,针对目前苹果 iPhone 15 Pro 手机过热问题进行了解读,并表示“与台积电 3nm 制程无关”。

郭明錤称,iPhone 15 Pro 系列的过热问题,与台积电的 3nm 制程无关,主要很可能是为了让重量更轻,因此对散热系统设计作出了妥协,像是散热面积较小、采用钛合金影响散热效果等。

当然,这话说得确实挑不出毛病,根据目前的拆解来看,iPhone 15 Pro依旧采用的双层主板,背部是ROM芯片,面前的是基带芯片,都是发热量较大的几颗芯片,把它们放到一起,无异于让A17 Pro待在篝火旁边,负载一大,火势就会变大,不仅处理器降频运行,用户也会很快就会感受到手机发热。

外加苹果在这次发布会上吹了很久的钛合金边框,实际上还变相加剧了iPhone散热差的毛病,钛的导热系数λ=15.24W/(m.K),约为镍的1/4,铁的1/5,铝的1/14,而各种钛合金的导热系数比纯钛的导热系数还有再下降约50%,这也就是说iPhone 15 Pro虽然轻了,但是散热反而不如iPhone 15的铝合金边框和iPhone 14 Pro的不锈钢边框。

但是郭明錤这番话也并不全面,根据极客湾的测试,iPhone 15 Pro和iPhone 15 Pro Max的续航时间相较于上一代,反而出现了倒退,下降了几十分钟左右,在电池容量微增的基础上,续航时间反而缩短,除了处理器本身性能调度原因外,问题恐怕还是出在了A17 Pro的本身的能效表现上了。

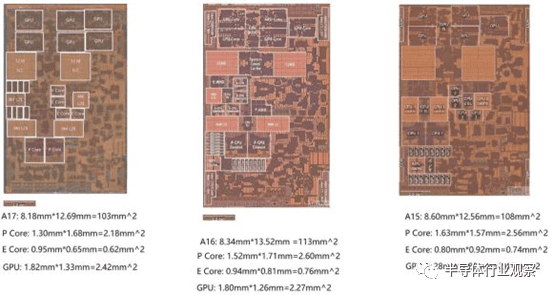

根据Techinsights的芯片拆解,与A16相比,A17 Pro 每颗性能核心和效率核心的面积减少了 20%,每个 GPU 核心的面积增加了 5%,整体 GPU 核心增加了 20%,且由于工艺制程的进步,A17 Pro芯片的整体面积略有缩小,但晶体管数量来到了新高,为190亿,对比上代的160亿晶体管,增加了近20%,能够完成如此大的升级,台积电3nm工艺功不可没。

图片来自:Techinsights

但根据苹果官方的公告,A17 Pro的CPU整体性能只是比上一代提升了约10%,提升幅度达到20%的GPU又有很大程度上是因为5核变6核,只有NPU提升幅度最大,算力从17TOPS升级到35TOPS,不难猜测它的实际规模变大了不少,外加新的USB 3控制器的加入,这些就是A17 Pro的主要升级点了,并未完成很多人预期里的大幅度跨越。

当A17 Pro褪去了神话光环之际,台积电的3nm也备受质疑。

FinFET气数已尽

为什么在4nm还顺风顺水的台积电,唯独到了3nm时却翻了车呢?

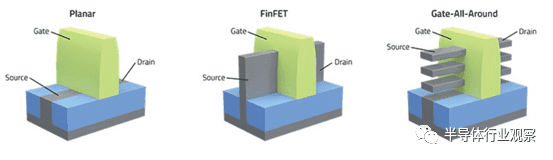

在5nm时,无论是台积电还是三星,都采用了FinFET(鳍式场效晶体管)的技术来控制流过晶体管的电流,这种技术能从“三面”来控制电子的通过(如下图),若电子没有被好好控制而乱跑,就会造成漏电,继而使手机的温度升高。

为选择更好地控制电流,两家半导体巨头都发展出从“四面”来控制电子通过的技术,称作GAA(Gate-All-Around),进一步防止漏电发生。但在3nm这一节点,台积电选择继续使用FinFET工艺,直到2纳米才转换成GAA,三星则抢先在3纳米时导入GAA,虽然目前还未大规模量产,但有望提供比FinFET更好的功耗与密度。

2011年,英特尔首度在Ivy Bridge 微架构处理器上应用22nm FinFET技术,2014年,台积电和三星首度在16/14nm工艺里导入FinFET工艺,在随后的几年时间当中,FinFET成为了众多晶圆厂热捧的技术,传统平面工艺无法满足先进制程的需求,摩尔定律再一次得到延续。

但没过几年,到了7nm制程以下,静态漏电的问题越来越大,原本制程演进的功耗和性能红利逐渐消失,FinFET无法满足3nm及更先进制程的需求已成为了大家的共识,何时导入GAA就成为很多人关心的重点,英特尔和台积电选择在3nm上继续沿用FinFET,而处于竞争劣势的三星下定决心,在3nm就引入GAA技术,力图争取到更多客户。

在2020年8月的台积电技术研讨会上,台积电表示,它已对其 FinFET 技术进行了重大更新,N3即3nm会使用 FinFET 的扩展和改进版本,性能增益高达 50%,功耗降低高达 30%,密度增益比 N5 提高 1.7 倍,不过这里需要注意的是,这部分对比仅仅是初代N3与N5的对比,在N5经过多轮迭代升级到最新的N4之后,实际提升并没有研讨会上公布的那么美妙。

回过头再来看GAA,台积电将其称为nanosheet FET,Intel称其为RibbonFET,这些技术本质都是一样的,就是把FinFET的fin转90°,然后把多个fin横向叠起来,这些fin都穿过gate——或者说被gate完全环抱,所以叫做gate all around;另外每个翻转过的fin都像是一片薄片(sheet),它们都是channel,因此也被称为nanosheet FET。

从结构上来看,GAAFET电晶体的gate与channel的接触面积变大了,且每一面均有接触,也就能够实现相比FinFET更好的开关控制。而且对于FinFET而言,fin的宽度是个定值;但对GAAFET而言,sheet本身的宽度与有效通道宽度是灵活可变的。更宽的sheet自然能够达成更高的驱动电流和性能,更窄的sheet则占用更小的面积。

台积电没在3nm用GAA的原因并不难理解,成本和技术。成本是新工厂新设施吃掉的资本投入,而技术呢,例如硅基通道中较低的空穴迁移率(hole mobility),导致pFET性能表现不佳。IBM在之前的IEDM上表示,这一问题的解决方法在于pFET可应用压缩应力的锗化硅(SiGe)通道材料:“pFET锗化硅通道能够实现40%的迁移率提升,相较硅基通道有10%的性能优势,而且有更低的阈值电压(Vt),负偏压温度不稳定性(NBTI)表现也有提升。”

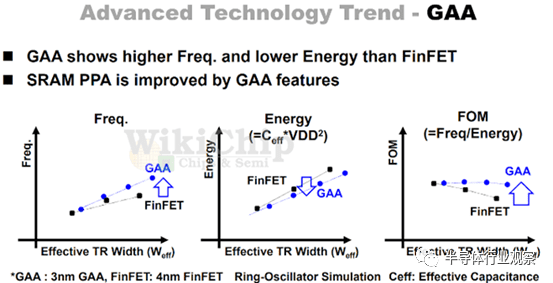

当然GAA的好处并不明显可能也是台积电的顾虑之一,三星此前谈到了3nm GAA制程,其比4nm FinFET在频率和功耗方面的优势,如下图所示,但图中并没有提供绝对值和相对值,其只是笼统地说,3nm GAA与4nm FinFET电晶体相比,在相同的有效通道宽度(Weff,fin/sheet的宽度× fin/sheet的个数)下,3nm GAA能够达成更高的频率;与此同时达成更低的功耗。

种种原因让台积电打定主意,在2nm才会使用GAA,3nm成为了最后一代FinFET,这也为A17 Pro的翻车埋下了伏笔。

更要命的当然还是良率问题,根据 Hi Investment & Securities 的数据,三星的 3 nm良率估计超过 60%,相比之下,台积电的 3 nm良率约为 55%,新技术的良率几乎与旧技术良率持平,让人不由想起了几个月前曝光的苹果与台积电之间的“甜心交易”:苹果向台积电下巨额 3nm 芯片订单,但是要求不合格芯片成本均由台积电自己承担,苹果只需要为良品芯片付费,有媒体表示,这样下来,苹果每年可节省数十亿美元。

如果良率足够高,苹果也没必要专程与台积电达成这项交易了,而台积电自2022年量产3nm至今,良率仍然没有到达苹果的底线,如今在能耗表现上也不理想,接下来能否说服更多客户接受这样一个价格再次上涨的工艺,或许才是台积电在2024年需要解决的大问题。

3nm谁领风骚?

目前,台积电为苹果代工的依旧是N3B即第一代3nm工艺,该工艺的好处是晶体管密度大幅增加,即A17 Pro实现的190亿晶体管,而明年登场的N3E,在晶体管密度上表现会稍逊一筹,但功耗控制方面更加理想,包括苹果在内的多家厂商都有意采用这项工艺,如果届时台积电能大幅提升良率,相信上门的Fabless厂商依旧会络绎不绝。

但三星早已拿着GAA的3nm虎视眈眈,一旦台积电犯下错误,原本属于它的订单就有可能流向老对手,而这样的局面早在16nm和7nm时就上演过,如今3nm悬而未决,未尝没有再发生一次的可能性。

3nm,是台积电亟需跨过的一道小坎。

参考文献

1. TSMC’s 3-nm Process Under Scrutiny Due to iPhone 15 Pro Overheating Issues——businesskorea

2. iPhone15 Pro的A17 Pro芯片照片,与A15/A16配置对比——iphone-mania

3. 跟三星不同调!台积电3纳米架构沿用FinFET,首席科学家黄汉森揭背后决策——bnext

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:邵逸琦