近日,一年一度的Hot Chips正式在斯坦福大学拉开帷幕。

据了解,Hot Chips的全称是A Symposium on High Performance Chips,于每年八月份在斯坦福大学举行。不同于其他行业会议以学术研究为主,Hot Chips是一场产业界的盛会,各大处理器公司会在每年的会上展现他们最新的产品以及在研的产品。

进入大会的第二天,我们不但看到了来自英特尔、AMD、Arm这些传统处理器巨头的展示,还看到了存储双雄三星和SK海力士的分享。此外,RISC-V服务器芯片新贵Ventana也在本届大会上分享了公司Veyron V1的细节。

在本文中,我们综合了这些巨头的产品,让大家对当前领先的处理器设计理念有所了解。

英特尔公布下一代处理器细节

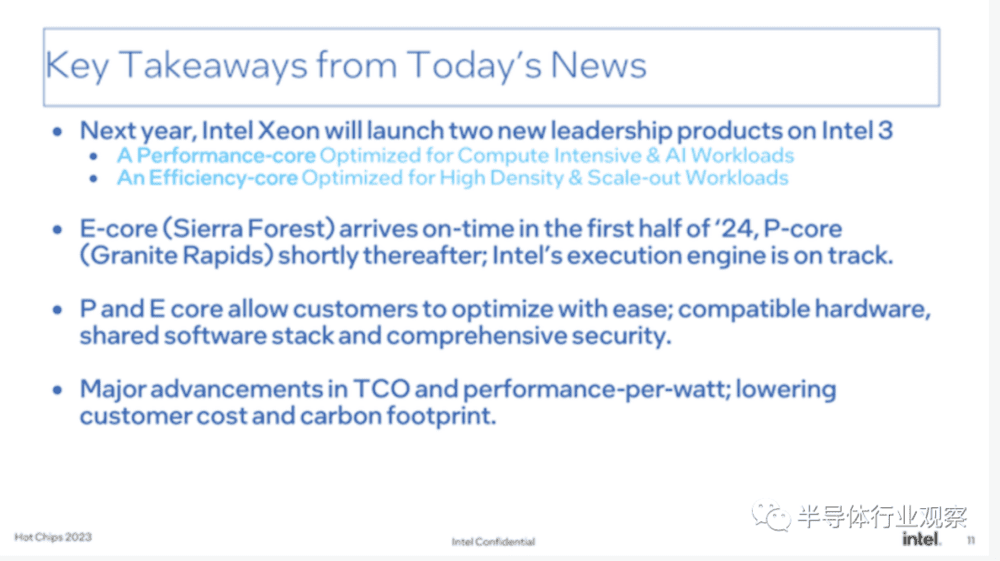

作为处理器领域当之无愧的巨头,英特尔在 Hot Chips 2023上分享了其下一代 Xeon 处理器 Granite Rapids 和 Sierra Forest的细节。根据之前的资料,这两款处理器将于 2024 年推出。英特尔此前曾在其数据中透露过这款处理器中心路线图——最近一次更新是在今年 3 月。在Hot Chips上,该公司提供了更多关于芯片及其共享平台的技术细节。

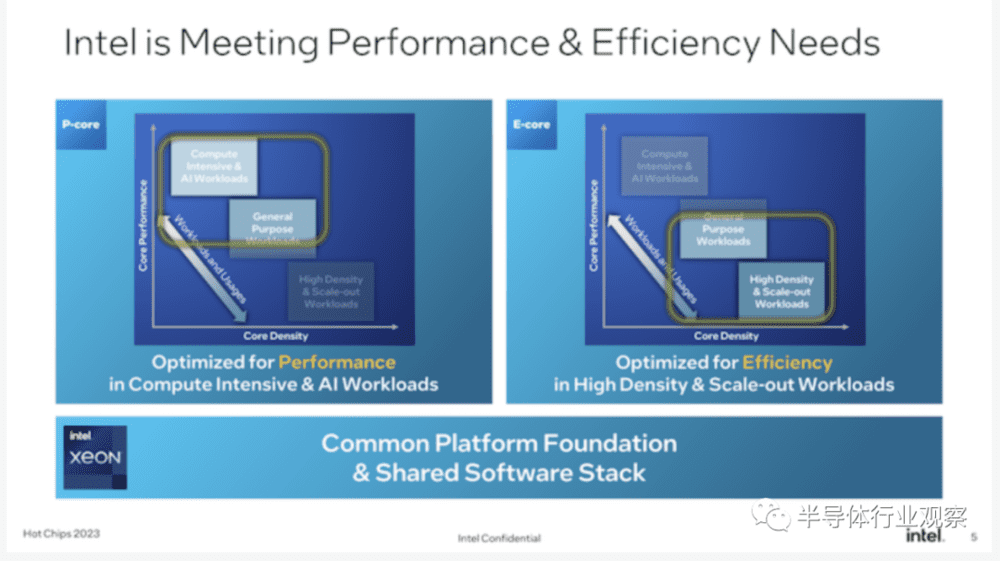

虽然英特尔至强处理器没有“不重要”一代的说法,但由于引入了面积高效的 E 核,Granite Rapids 和 Sierra Forest 有望成为英特尔至强可扩展硬件生态系统最重要的更新之一。

自第 12代酷睿(Alder Lake)以来,它已经成为英特尔消费处理器的中流砥柱,而即将推出的第 6代至强可扩展平台最终将把 E 核引入英特尔的服务器平台。尽管与两种核心类型混合在单个芯片中的消费类零件不同,英特尔正在采取纯粹的同质策略,为我们提供全 P 核 Granite Rapids 和全 E 核 Sierra Forest。

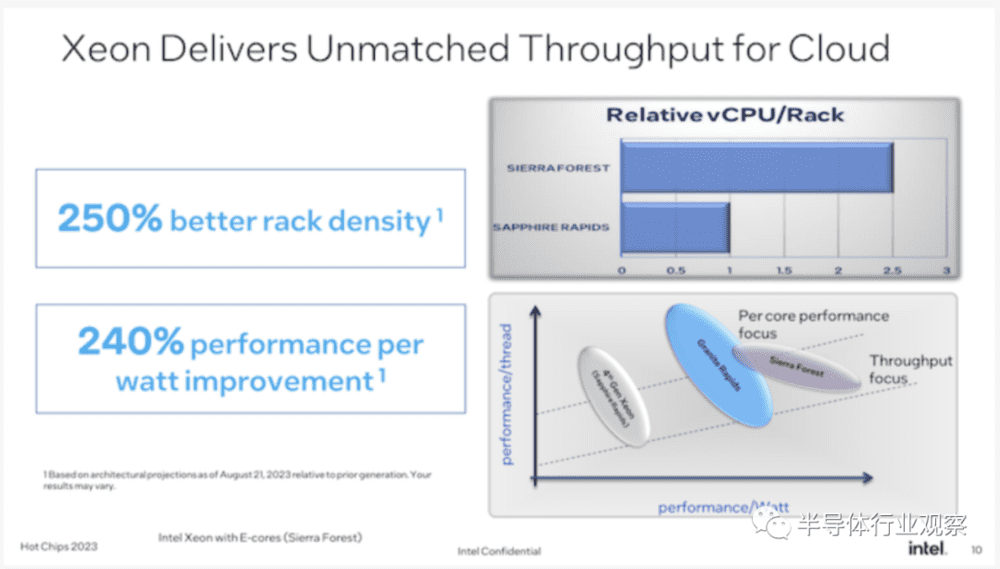

作为英特尔首款供数据中心使用的E核至强可扩展芯片,Sierra Forest可以说是这两款芯片中最重要的一款。恰如其分的是,它是英特尔基于 EUV 的intel 3 工艺节点的主导产品,也是首款推出的至强处理器。据该公司称,它仍有望在 2024 年上半年发布。与此同时,Granite Rapids 将“很快”落后于这一点,采用相同的 Intel 3 工艺节点。

由于英特尔计划在一代中提供两个截然不同的 Xeon,因此第六代 Xeon 可扩展平台的一个重要因素是两个处理器将共享相同的平台。这意味着相同的插槽、相同的内存、相同的基于小芯片的设计理念、相同的固件等。虽然仍然存在差异,特别是在 AVX-512 支持方面,但英特尔正在尝试制造这些芯片尽可能互换。

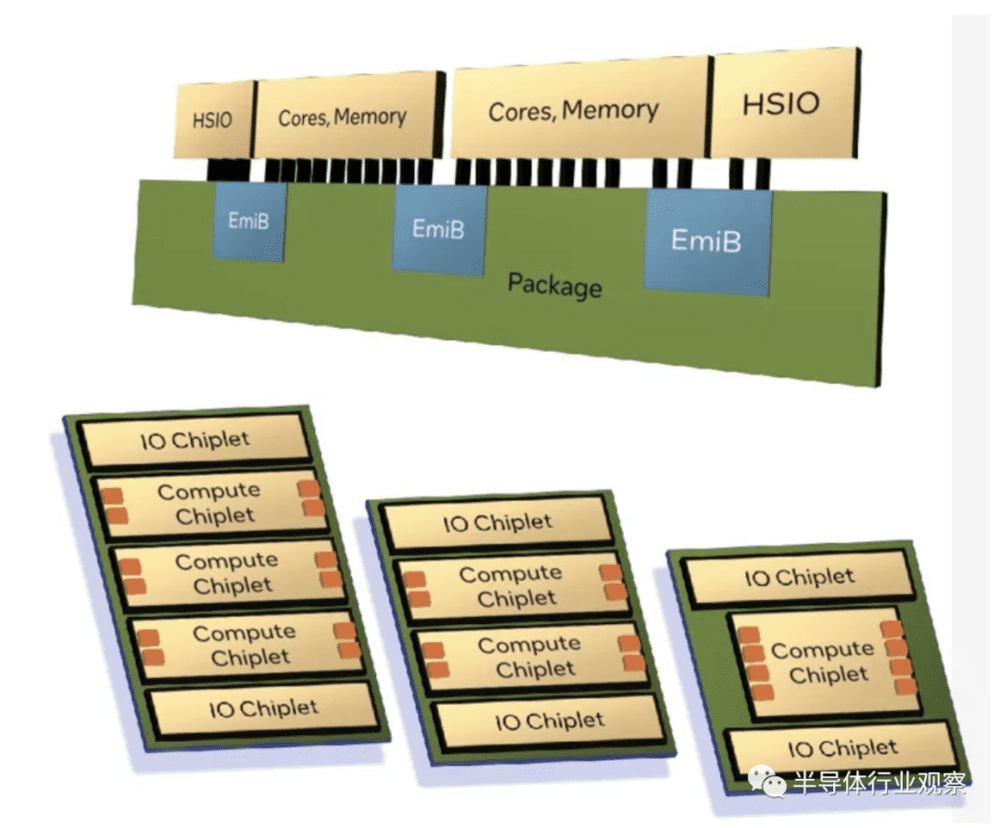

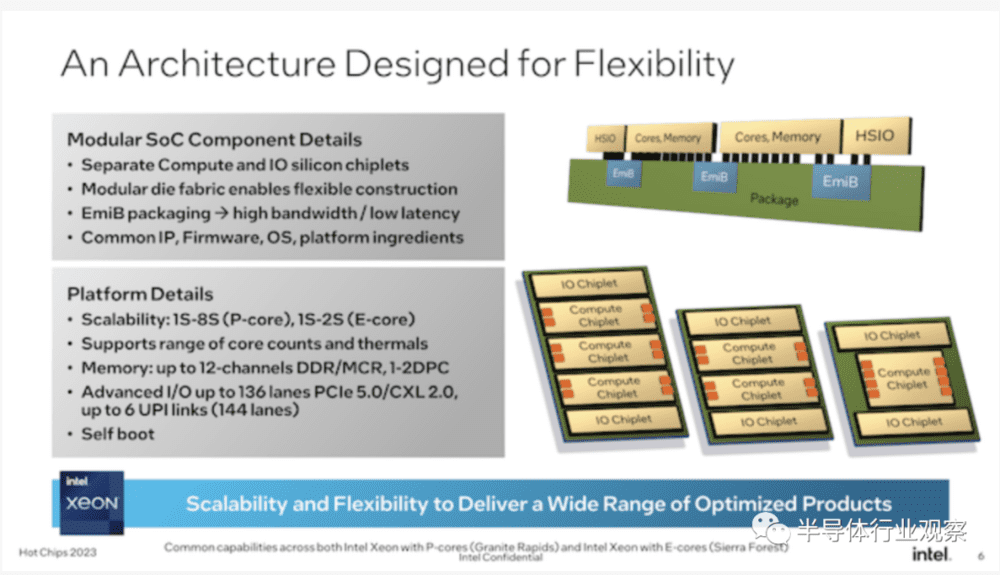

正如英特尔宣布的那样,Granite 和 Sierra 都是基于小芯片的设计,依赖于计算和 I/O 小芯片的混合,这些小芯片使用英特尔的有源 EMIB 桥接技术缝合在一起。虽然这并不是英特尔在 Xeon 领域首次与小芯片共舞(XCC Sapphire Rapids 获得了这一荣誉),但这是小芯片设计的一次独特演变,它使用了不同的计算/IO 小芯片,而不是将其他“完整”的 Xeon 小芯片拼接在一起。除此之外,这意味着 Granite 和 Sierra 可以共享通用的 I/O 小芯片(基于 Intel 7 工艺构建),从制造的角度来看,Xeon 是 Granite 还是 Sierra “仅仅”是哪种类型的问题计算小芯片已放下。

值得注意的是,英特尔首次确认第六代至强可扩展平台正在获得自启动功能,使其成为真正的 SoC。由于英特尔将操作所需的所有必要 I/O 功能都放置在 I/O 小芯片中,因此不需要外部芯片组(或 FPGA)来操作这些处理器。这使得英特尔的 Xeon 系列在功能上更接近 AMD 的 EPYC 系列,AMD 的 EPYC 系列已经具有类似的自启动功能一段时间了。

总而言之,第六代至强可扩展平台将支持多达 12 个内存通道,并可根据现有计算芯片的数量和功能进行扩展。正如英特尔之前透露的那样,该平台将是第一个支持新的多路复用器组合列(MCR:Multiplexer Combined Ranks)DIMM 的平台,该平台本质上是将两组/列内存芯片组合在一起,以使进出 DIMM 的有效带宽加倍。英特尔表示,凭借更高的内存总线速度和更多的内存通道,该平台可以提供比当前 Sapphire Rapids Xeon 多 2.8 倍的带宽。

至于 I/O,最大配置 Xeon 将能够提供多达 136 个通道的通用 I/O,以及多达 6 个 UPI 链路(总共 144 个通道)用于多插槽连接。对于 I/O,该平台支持 PCIe 5.0(为什么不支持 PCIe 6.0?我们被告知时机不合适)以及更新的CXL 2.0标准。与英特尔大核 Xeon 的传统情况一样,Granite Rapids 芯片将能够总共扩展到 8 个插槽。另一方面,由于正在使用的 CPU 核心数量以及英特尔对其客户的不同用例的期望,Sierra Forest 将只能扩展到 2 个插槽。

除了共享平台的详细信息外,英特尔还首次提供了 E 核和 P 核所用架构的高级概述。正如现在多代 Xeon 的情况一样,英特尔正在利用与其消费部件相同的基本 CPU 架构。因此,Granite 和 Sierra 可以被认为是解构的 Meteor Lake 处理器,Granite 配备 Redwood Cove P 核心,而 Sierra 配备 Crestmont E 核心。

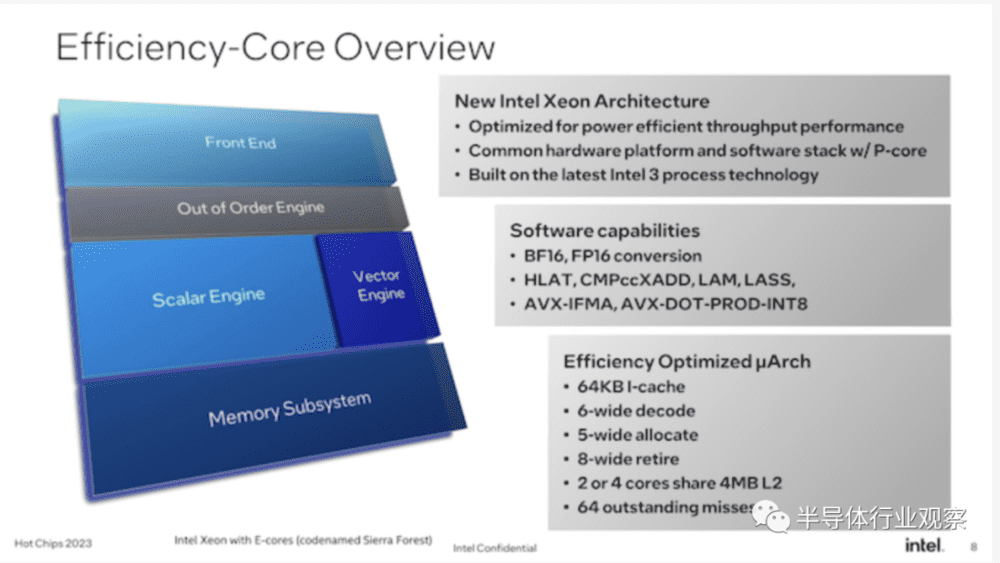

如前所述,这是英特尔首次尝试为 Xeon 市场提供 E 核心。对于英特尔来说,这意味着要针对数据中心工作负载调整其 E 核心设计,而不是定义上一代 E 核心设计的以消费者为中心的工作负载。

虽然没有深入探讨架构本身,但英特尔透露 Crestmont 正在提供 6 宽指令解码路径(instruction decode pathway)以及 8 宽 retirement backend。虽然不如英特尔的 P 核心强大,但 E 核心绝不是轻量级核心,英特尔的设计决策反映了这一点。尽管如此,它的设计在芯片空间和能耗方面都比 Granite 中的 P 核心要高效得多。

Crestmont 的 L1 指令高速缓存(I 高速缓存)将为 64KB,是早期设计中 I-cache大小的两倍。英特尔很少触及 I-cache 容量(由于平衡命中率和延迟),因此这是一个显着的变化,一旦英特尔更多地谈论架构,看到其后果将会很有趣。

与此同时,Crestmont E-core 系列的新成员可以将这些核心打包成 2 或 4 核集群,这与目前仅提供 4 核集群的 Gracemont 不同。这本质上就是英特尔将如何调整二级缓存与CPU核心的比例;无论配置如何,2 核集群都具有 4MB 共享 L2,每个核心为每个核心提供的 L2 数量是其他方式的两倍。这实质上为英特尔提供了另一个调整芯片性能的旋钮;需要稍高性能的 Sierra 设计(而不仅仅是最大化 CPU 核心数量)的客户可以使用更少的核心,同时获得更大的二级缓存带来的更高性能。

最后,对于 Sierra/Crestmont,该芯片将提供与 Granite Rapids 尽可能接近的指令。这意味着 BF16 数据类型支持,以及对各种指令集的支持,例如 AVX-IFMA 和 AVX-DOT-PROD-INT8。除了 AMX 矩阵引擎之外,您在这里找不到的唯一东西是对 AVX-512 的支持;英特尔的超宽矢量格式不属于 Crestmont 功能集的一部分。最终,AVX10 将有助于解决这个问题,但目前这已经是英特尔能够在两个处理器之间达到同等水平的最接近的了。

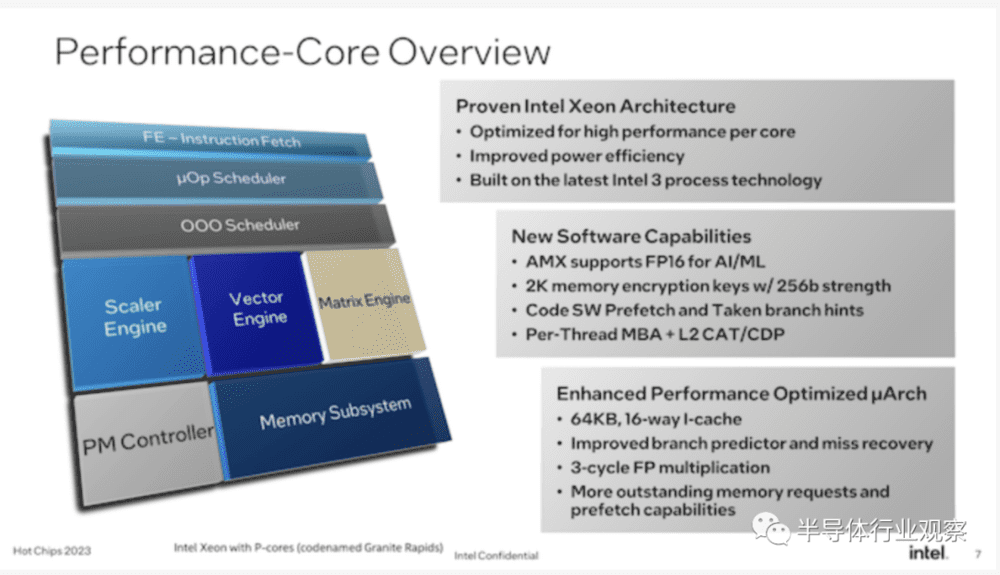

同时,对于 Granite Rapids,我们有 Redwood Cove P 核心。Redwood/Granite 是 Xeon 处理器的传统核心,对于英特尔来说,变化并不像 Sierra Forest 那样大。但这并不意味着他们袖手旁观。

在微架构方面,Redwood Cove 获得了与 Crestmont 相同的 64KB I-cache,容量是其前身的 2 倍。但最值得注意的是,英特尔成功地进一步降低了浮点乘法的延迟,将其从 4/5 个周期减少到仅 3 个周期。像这样的基本指令延迟改进很少见,因此我们总是欢迎看到它们。

除此之外,Redwood Cove 微架构的其余亮点是分支预测和预取,这是英特尔的典型优化目标。他们可以采取的任何措施来改进分支预测(并降低罕见失误的成本),往往会在性能方面带来相对较大的红利。

Redwood Cove 的 AMX 矩阵引擎获得了 FP16 支持,尤其适用于 Xeon 系列。FP16 的使用不如已支持的 BF16 和 INT8 那么多,但它总体上改进了 AMX 的灵活性。

内存加密支持也正在得到改进。Granite Rapids 的 Redwood Cove 版本将支持 2048 个 256 位内存键(memory keys),而 Sapphire Rapids 则支持 128 个键。高速缓存分配技术 (CAT) 以及代码和数据优先级(CDP)功能也得到了一些增强,英特尔将它们扩展为能够控制进入 L2 高速缓存的内容,而不仅仅是之前的 LLC/L3 高速缓存实施。

最终,不言而喻的是,英特尔相信他们即将推出的 Xeon 处理器将在 2024 年及以后做好准备。通过提高高端 P 核 Xeon 的性能,同时为只需要大量更轻的 CPU 内核的客户推出 E 核 Xeon,英特尔相信他们可以通过共享一个通用平台的两种 CPU 内核类型来满足整个市场的需求。

虽然现在谈论 Granite Rapids 和 Sierra Forest 的各个 SKU 还为时过早,但英特尔告诉我们,核心数量总体正在增加。Granite Rapids 部件将提供比 Sapphire Rapids 更多的 CPU 内核(SPR XCC 为 60 个),当然,Sierra 的 144 个内核将提供更多的 CPU 内核。但值得注意的是,英特尔不会按核心数量来划分这两个 CPU 系列——Sierra Forest 也将提供较小核心数量的产品(与 AMD 的 EPYC Zen4c Bergamo 芯片不同)。这反映了 P 和 E 核心的不同性能能力,毫无疑问,英特尔希望充分拥抱使用小芯片带来的可扩展性。

虽然 Sierra Forest 已经采用 144 个 CPU 核心,但英特尔还在我们的预简报中发表了一个有趣的评论,即他们的首款 E 核至强可扩展处理器的核心数量本可以更高。但该公司决定更加优先考虑每个核心的性能,从而产生我们明年将看到的芯片和核心数量。

最重要的是,英特尔正在强调他们的下一代 Xeon 处理器仍有望在 2024 年推出。英特尔刚刚从 Sapphire Rapids 的大规模延误(以及 Emerald Rapids 的连锁反应)中恢复过来,因此该公司热衷于向客户保证 Granite Rapids 和 Sierra Forest 是英特尔的时机重回正轨的地方。在之前的 Xeon 延迟和花了很长时间才将 E 核 Xeon 可扩展芯片推向市场之间,英特尔并没有像以前那样在数据中心市场占据主导地位,因此 Granite Rapids 和 Sierra Forest 将标志着一个重要的拐点英特尔数据中心产品的未来发展。

AMD Siena闪亮登场

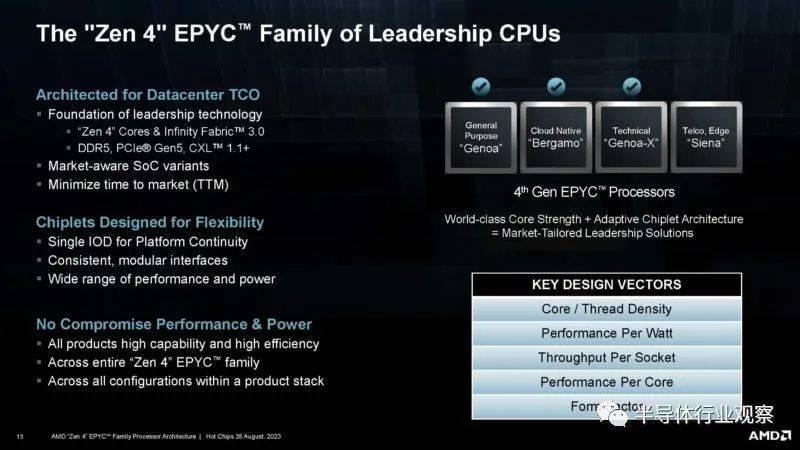

在 Hot Chips 2023 上,AMD 详细介绍了 AMD EPYC Genoa、Genoa-X 和 Bergamo CPU。它还在演讲中展示了即将推出的 Siena 平台的关键规格。

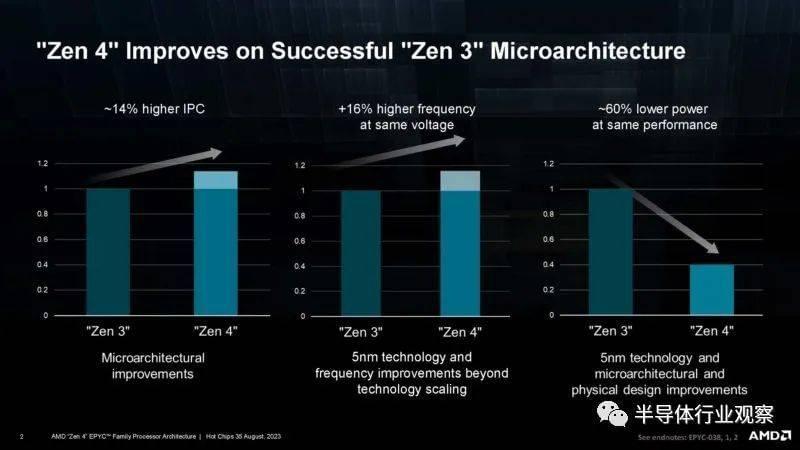

我们知道,AMD Zen 4 是AMD EPYC 7003“Milan”中使用的 Zen 3 的重大升级,具有更高的 IPC、更多的时钟和更低的功耗。

Zen 4c 则为Bergamo带来了更加紧凑的 Zen 4 核心。即便如此,AMD 仍然专注于制造大型 CPU。在Hot Chips上,他们就展示了一种低端解决方案。

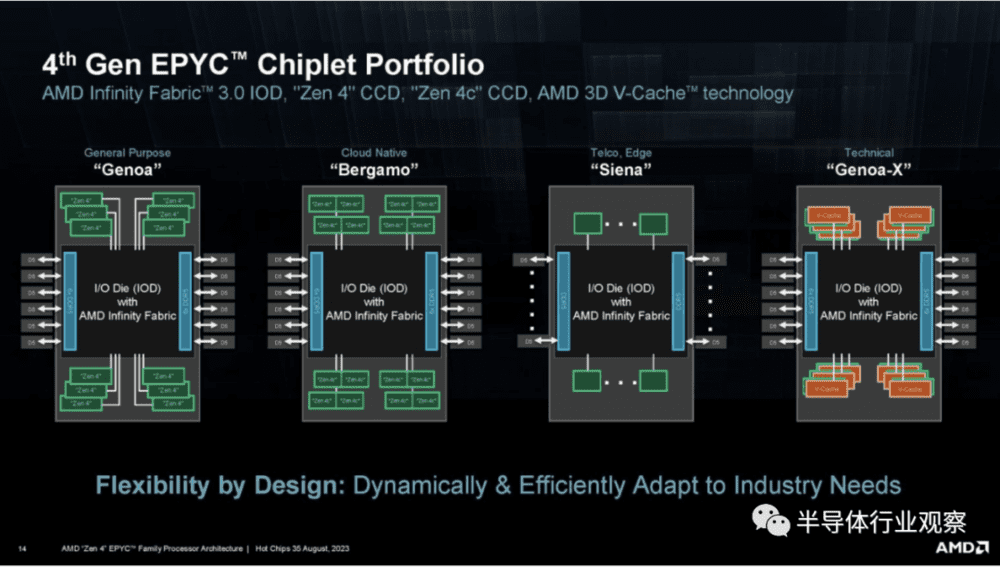

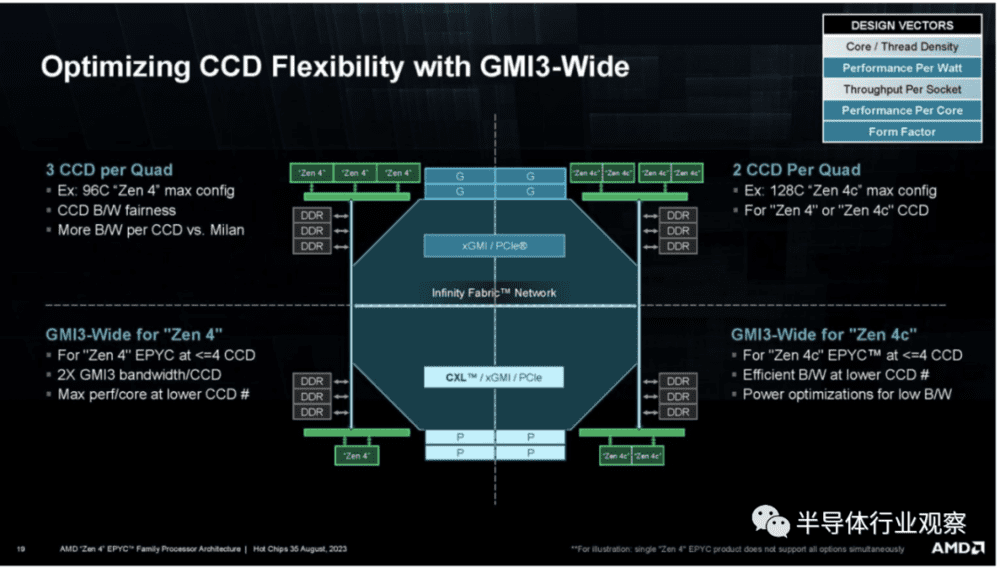

AMD 的 Socket SP5 策略是构建不同的小芯片并将它们与通用 I/O 芯片结合起来。

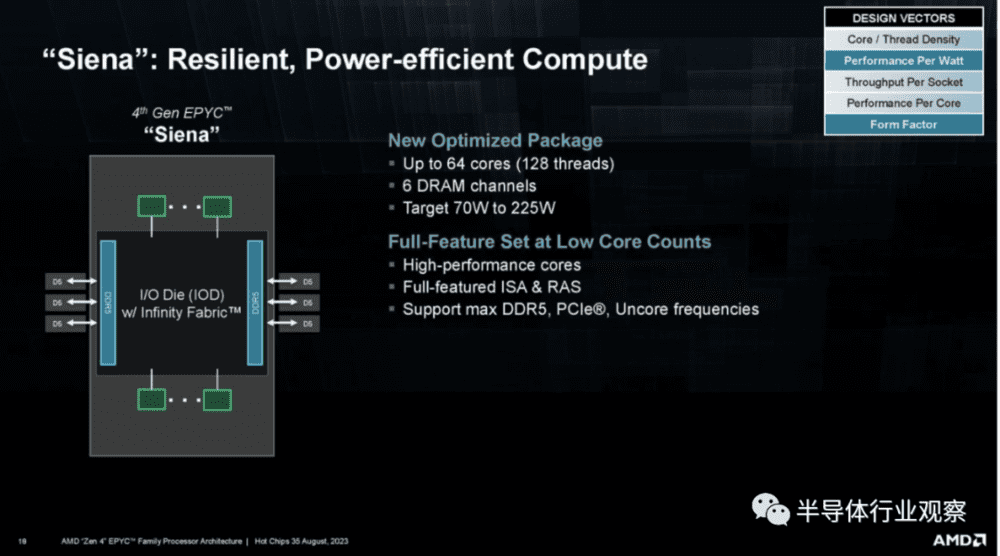

现在,AMD 展示了第四代 AMD EPYC 产品组合的第四个成员,即面向电信边缘市场的 Siena。

迄今为止,我们对Genoa的披露最多。我们最多只有 64 个内核和 6 个 DDR5 DRAM 通道。Siena 的规模将远低于 Genoa,TDP 为 70W 至 225W,尽管没有英特尔的某些 Xeon D 部件那么低。

AMD 需要较低功耗的部件,因为英特尔拥有其单片芯片 Sapphire Rapids 部件,该部件对于 32 核及以下的核心非常有吸引力,这是市场上的主要销量细分市场。96 或 128 核 350W+ 很棒,但它们不适合需要低于 150W CPU 的应用。

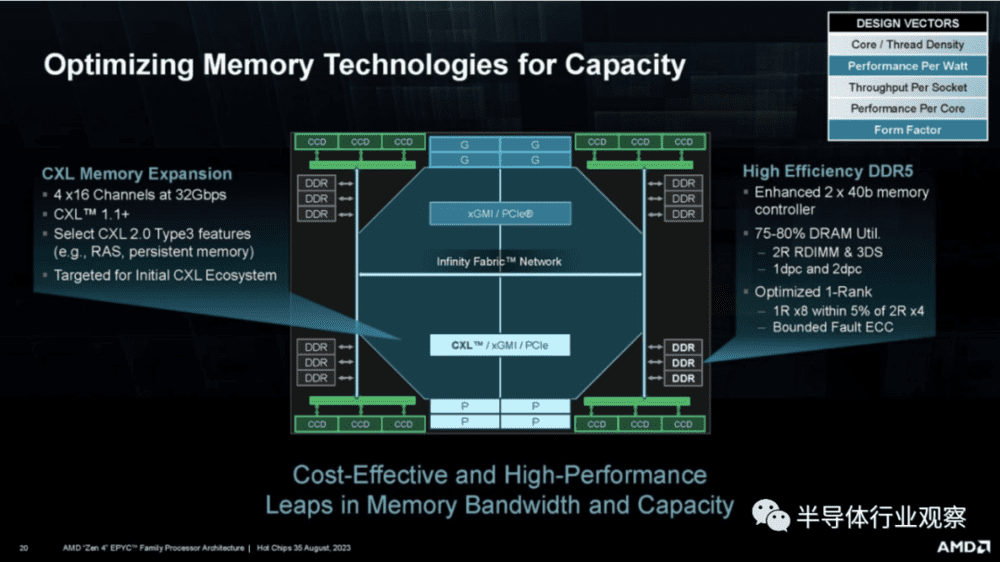

AMD 还展示了一张有趣的 CCD 幻灯片,展示了 I/O 芯片的一些功能。

这是一张很棒的幻灯片。AMD 还拥有一项内存技术,包括 CXL。

我们对 AMD EPYC Siena 的推出感到非常兴奋,因为 AMD 在低功耗领域的服务器产品组合中存在很大的漏洞。我们终于看到 AMD 如何利用一半的 DDR5 通道和更少的核心来实现这一目标。

Arm带来两款处理器

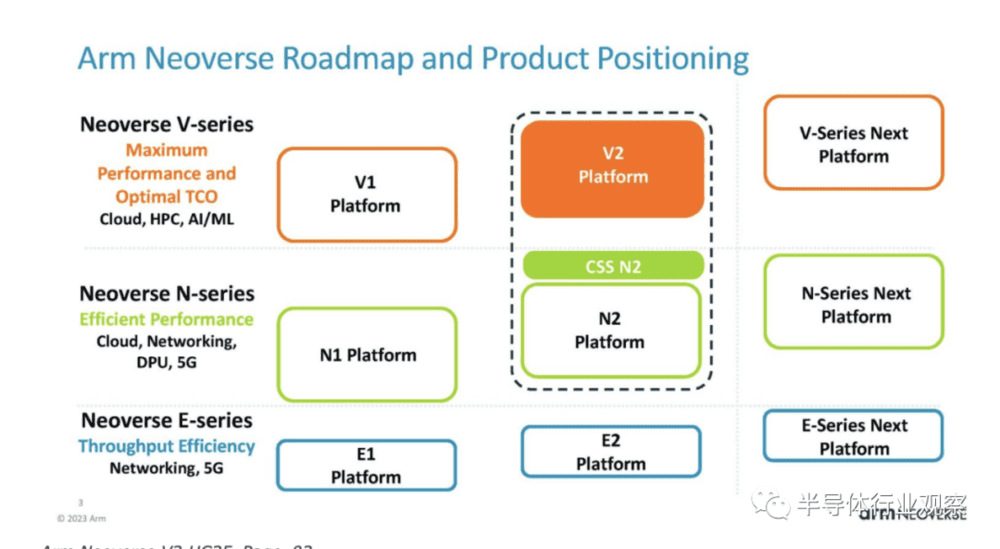

在今年的Hot Chips上,Arm带来了Arm Neoverse V2和Neoverse N2的更多分享。

Arm Neoverse V2 是当前一代 Neoverse 解决方案的一部分。Arm 致力于为数据中心和基础设施市场提供参考核心。Neoverse V2更多的是高性能数据中心CPU核心,而N2更多的是基础设施。

我们之前介绍过 Neoverse V2,其目标是提高 AWS 等公司在 Graviton 系列中使用的 Neoverse V1 设计的性能。

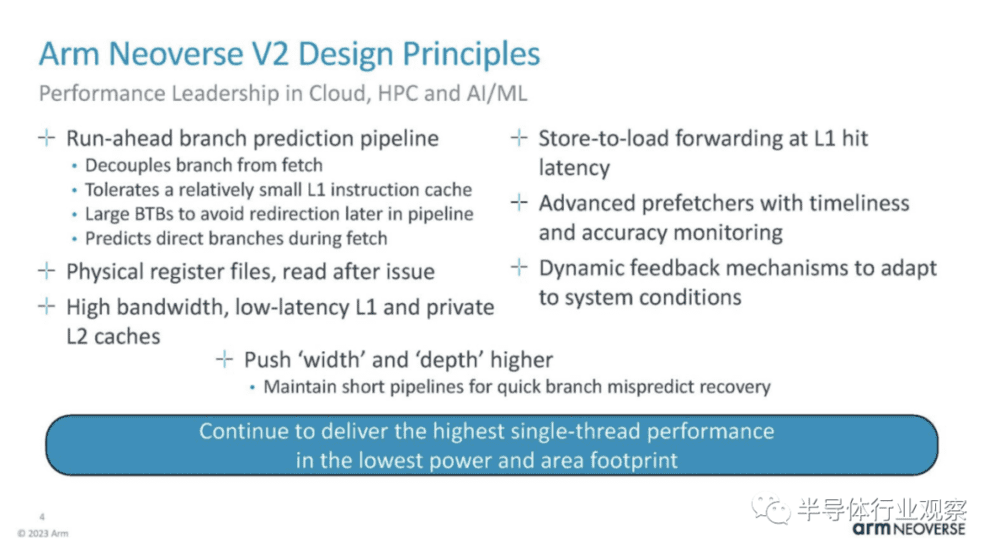

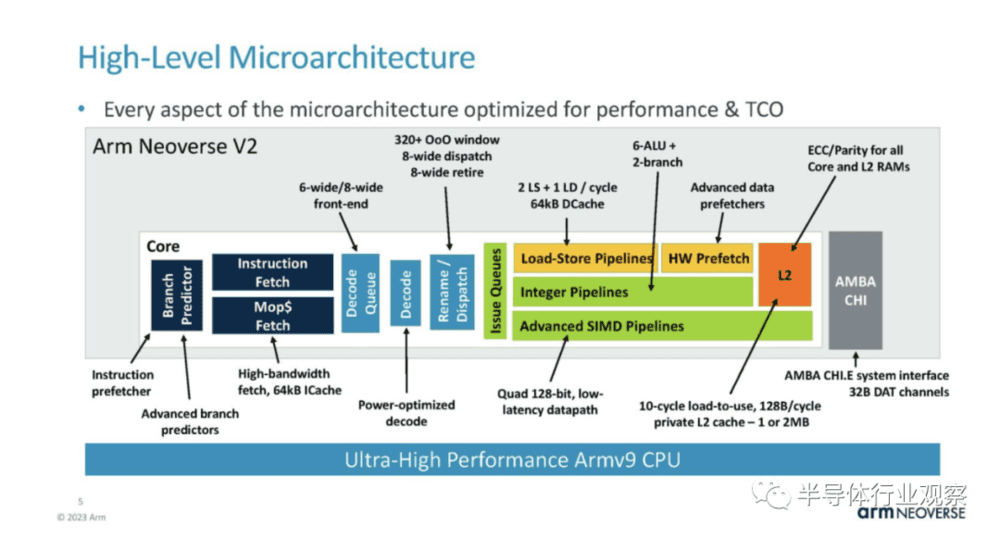

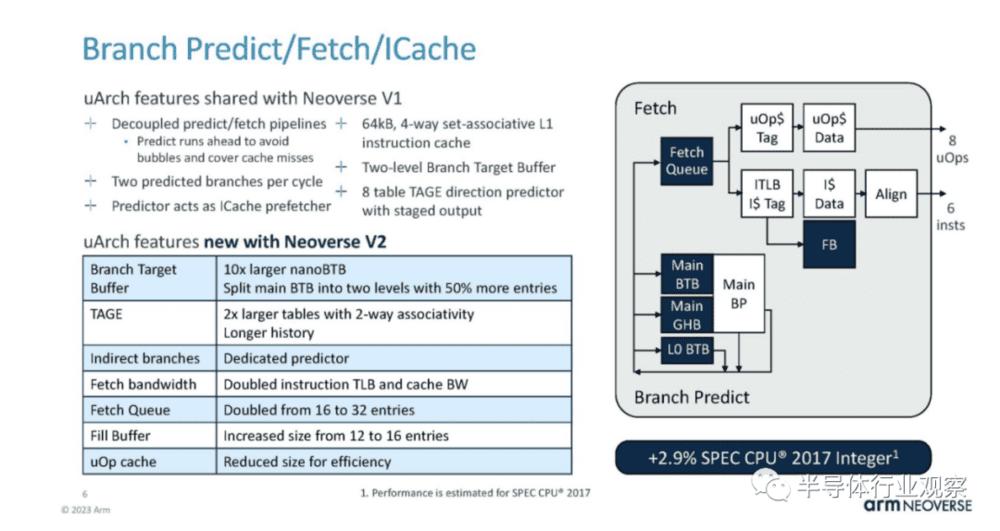

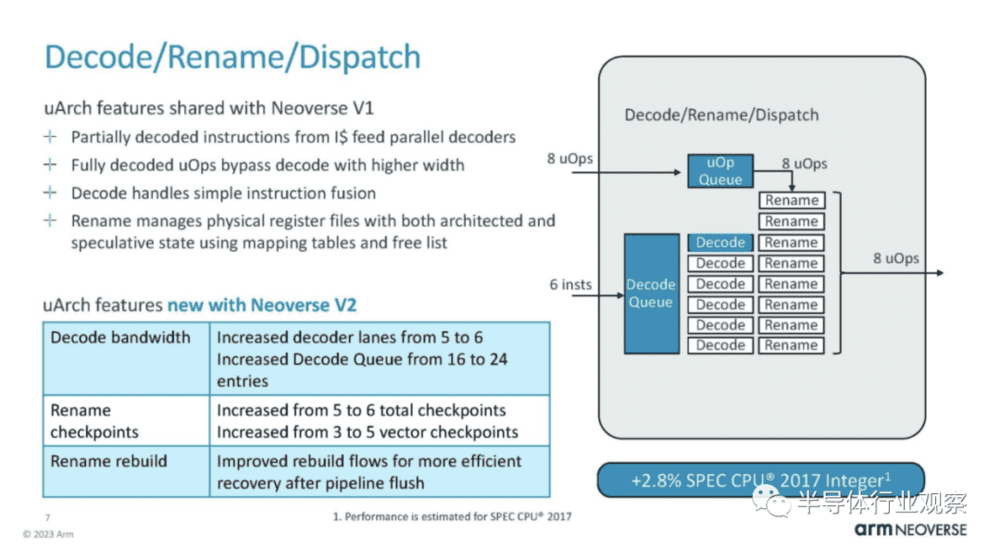

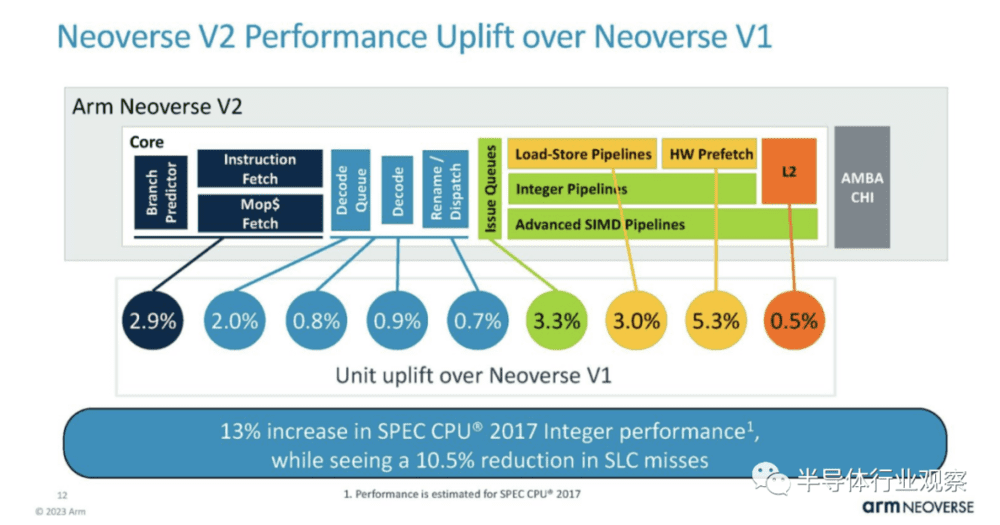

Arm Neoverse V2 是 Armv9 架构。这是一张显示核心部分亮点的图表。

在分支上,预测/获取/ICache 与 Neoverse V1 部分共享,但有一些重大改进。Arm 在每个部分都展示了这些变化对性能的影响,这非常酷。

这是V2的主题。它主要基于V1不断升级并提供更多资源。

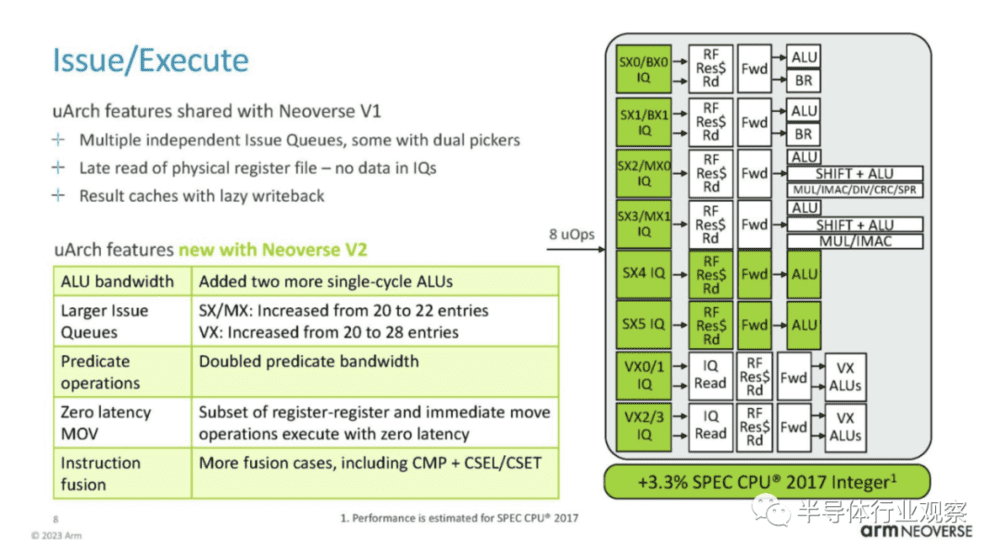

问题/执行方面是 V2 中的一个重大变化。

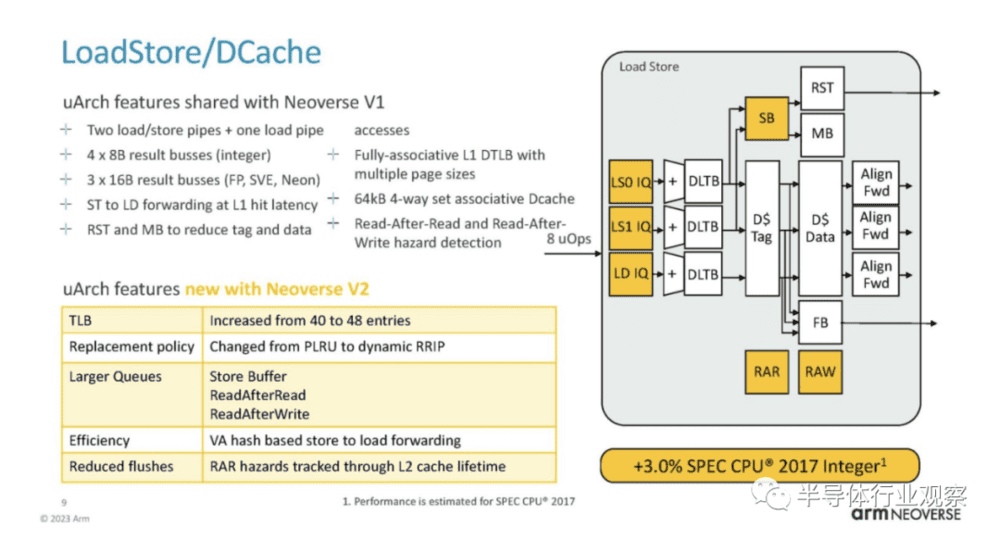

Load/Store 和 DCache 发生了变化,例如 TLB 增加了 20%。

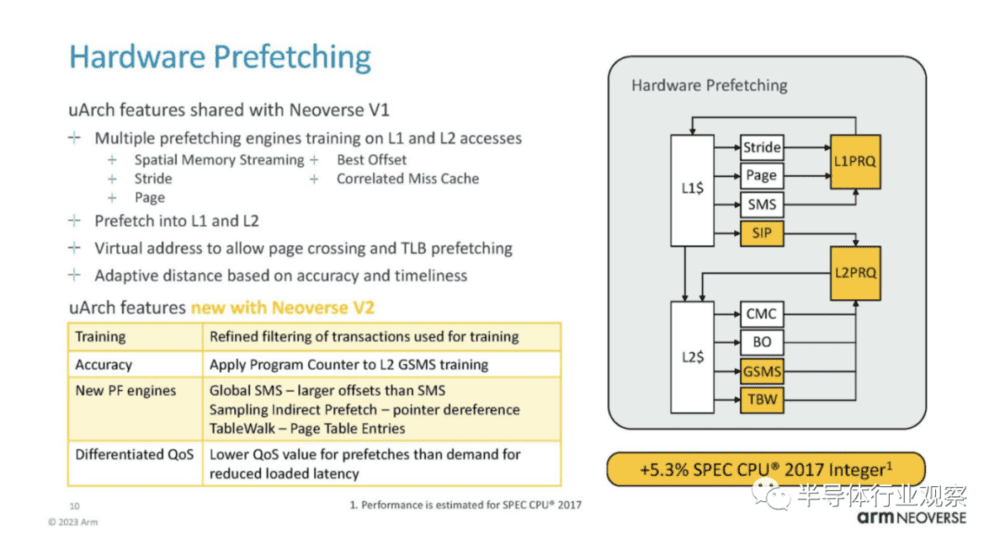

这也意味着 Arm 需要改进内核的硬件预取,以保持执行单元和缓存的运行。

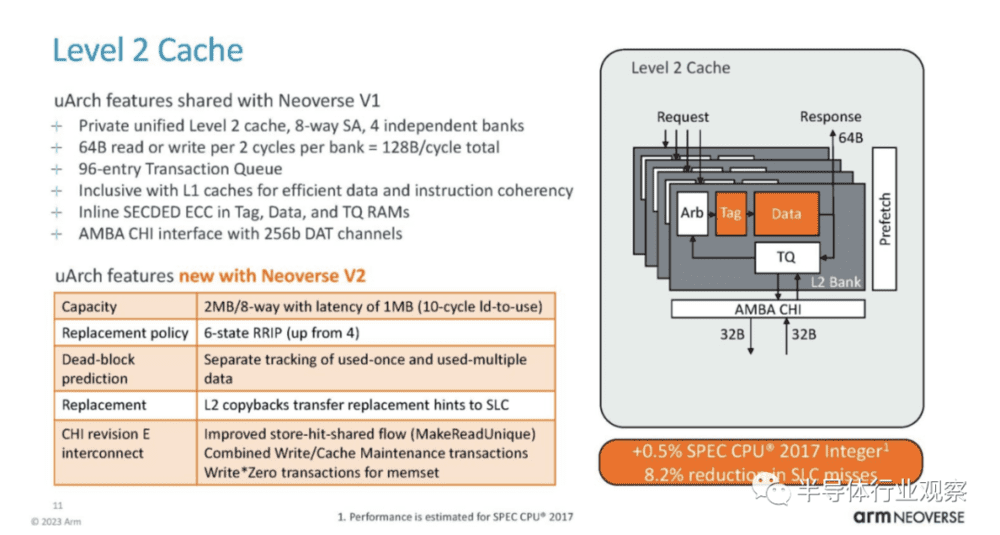

L2 缓存是每个核心私有的,是数据中心的重要特性。这是一个较小的 SPEC Int 增益区域。

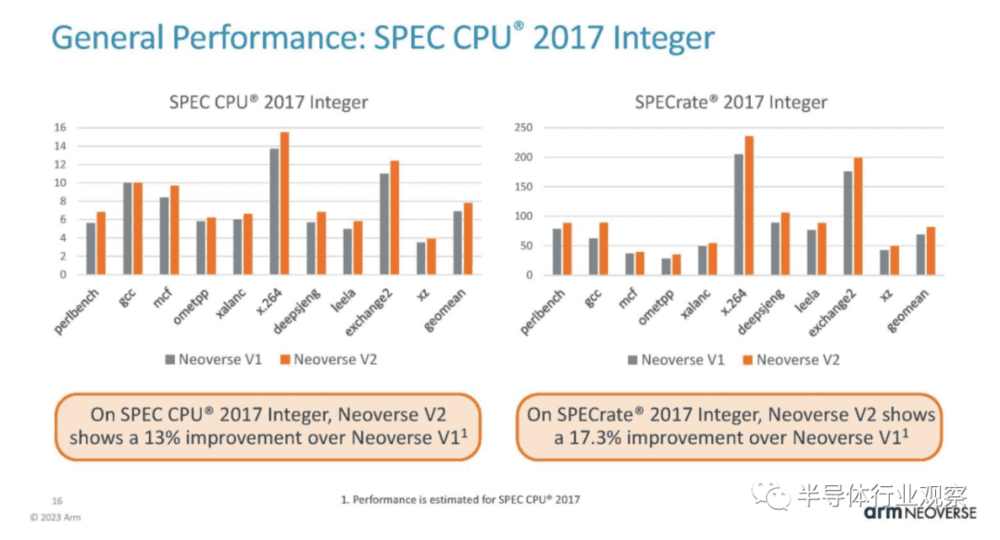

Arm 表示,与 V1 相比,这些 V2 变化综合起来使每个内核的性能提高了约 13%。如果添加的话,每个部分的数字并不等于 13% 的增长。这是因为某些变化会影响其他变化,因此总数小于每个单独改进领域的总和。

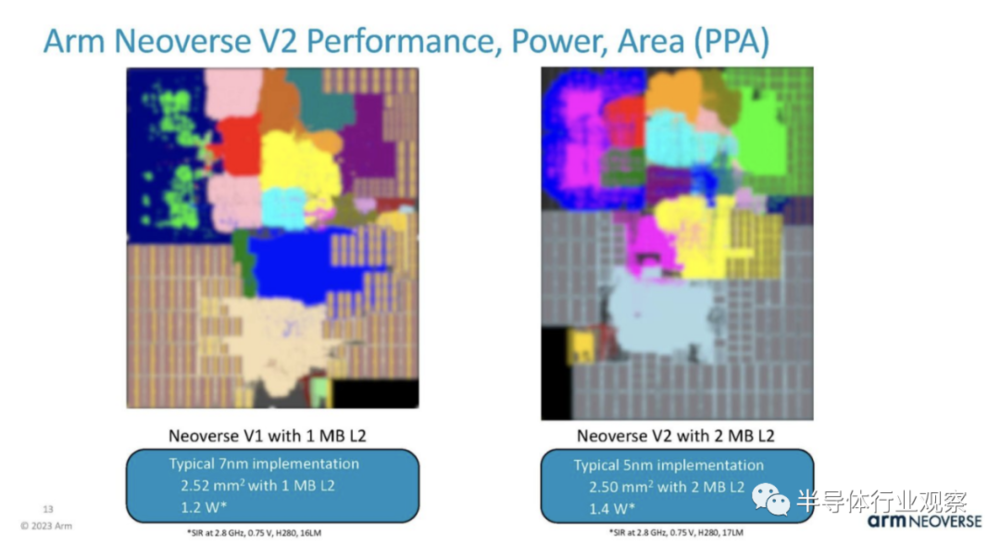

Arm 表示,新内核从台积电 7 纳米缩小到 5 纳米,尽管 L2 缓存增加了一倍,但功耗仅增加了约 17%,面积也大致相同。有趣的是,上面幻灯片中的 Arm 表示 V2 快了 13%,但下面的幻灯片使用了 16.666% 的功率。

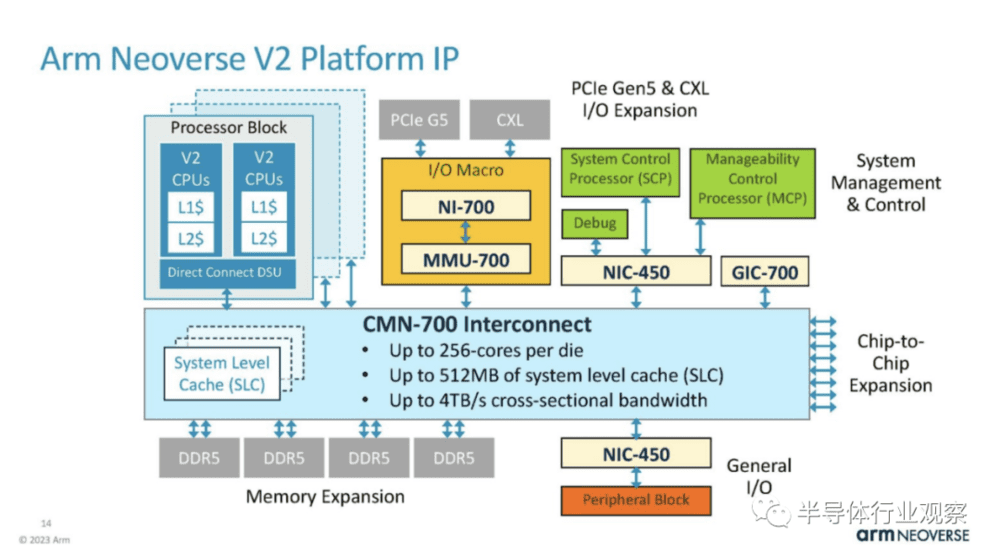

除了 V2 内核本身之外,该平台还具有 CMN-700 互连等功能,可提供更多缓存并增加内核数量。对于 Arm Neoverse 内核,这是内核,而不是整个芯片,因此需要采购 PCIe Gen5 IP 等项目。

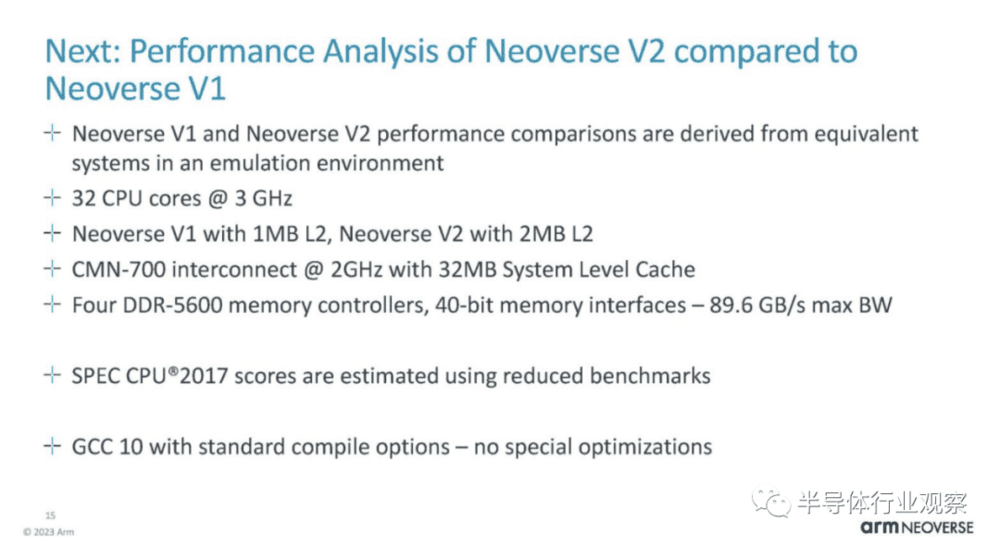

以下是性能结果的假设:

Arm 正在展示其整数性能。在预简报电话会议上,分析师询问了两个估计结果之间的差异,因为右侧图表标记为“SPECrate”,但都没有标记为基础或峰值。Arm 无法证实这一点。我们最好的猜测是,左图是基础图,右图是峰值图,但这只是猜测,因为 Arm 无法确认他们所显示的内容。

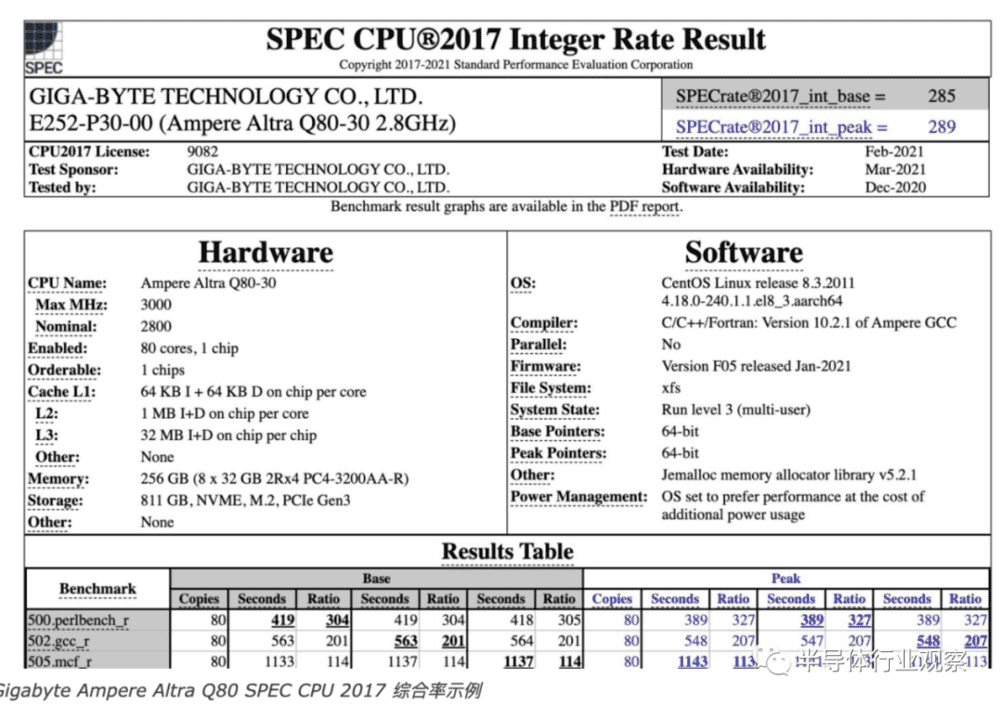

这些结果只是估计值,但以下是实际提交的结果,其中结果标有基线和峰值。令人惊奇的是,CPU 公司竟然无法回答这个问题。

这里是 Memcached,它通常较少受 CPU 限制,但较多内存/缓存限制。它是另一个整数,而不是浮点工作负载。因此,它通常在 Arm CPU 上表现良好。

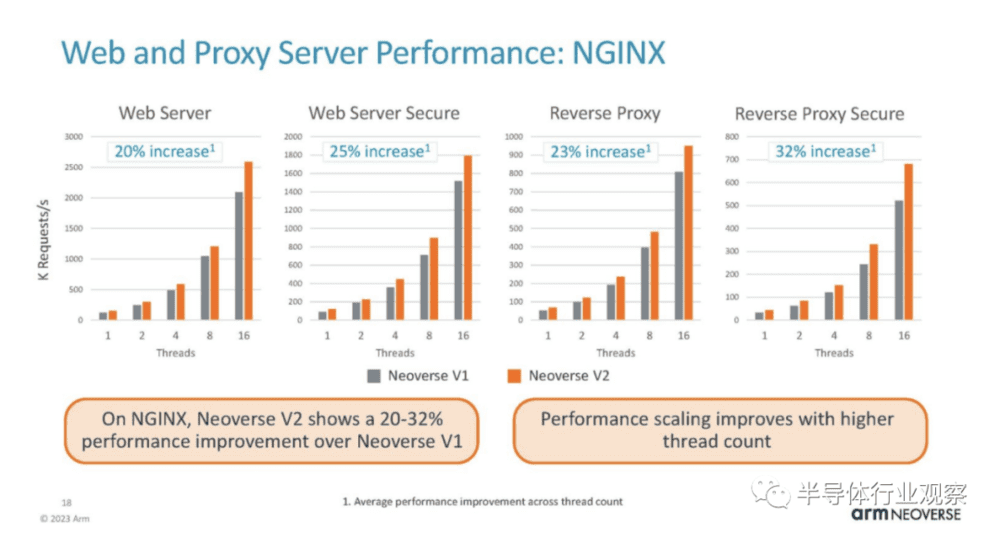

Nginx 是一种流行的 Web 服务器。这是另一个以整数为主的模型,因此一直是显示 Arm 服务器性能的支柱。

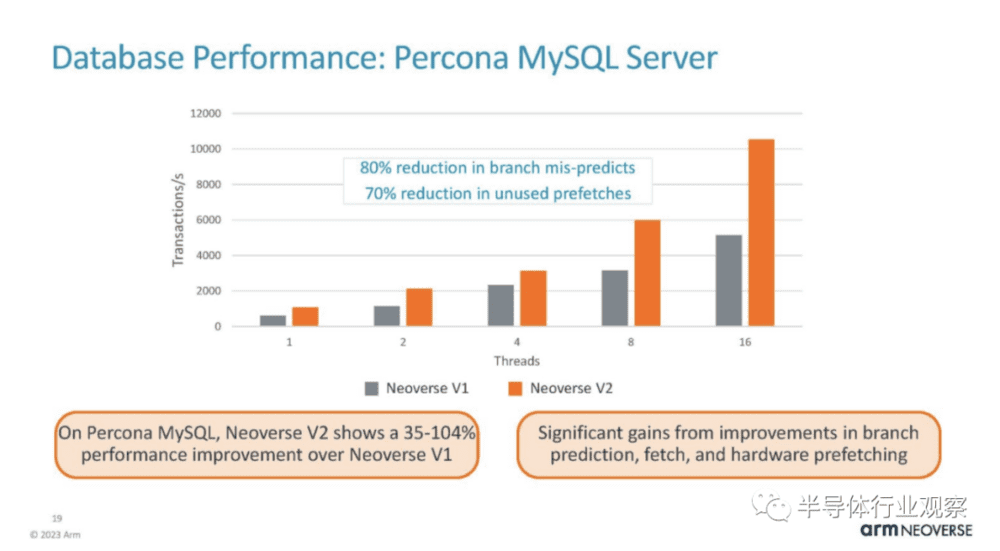

这是整数工作负载基准测试的另一个趋势。这一个得到了更大的推动。

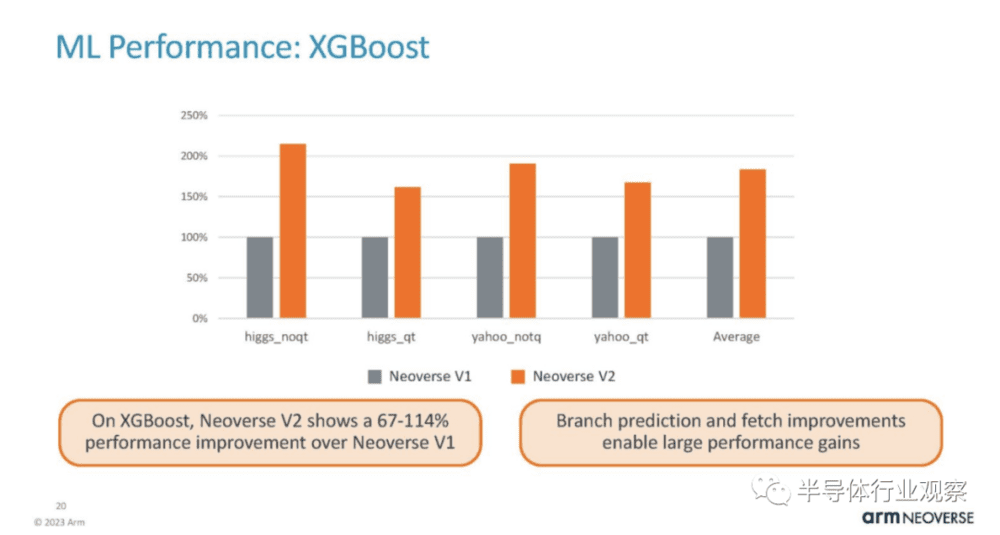

这是 XGBoost 性能。

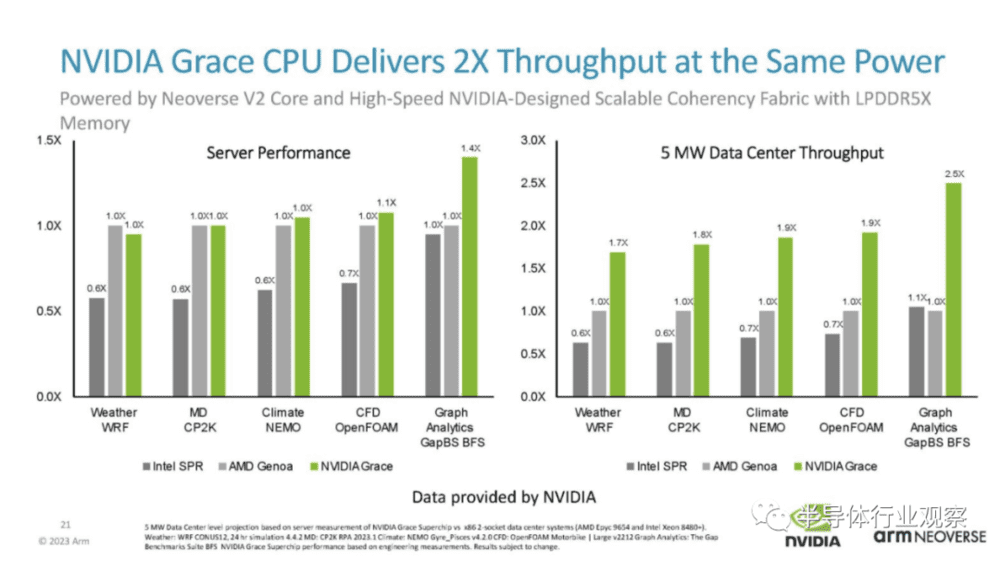

NVIDIA Grace Superchip 和 Grace Hopper 均使用该技术。这些主要是内存带宽敏感的工作负载。Grace Superchip 的正确比较应该是 Intel Xeon Max 和Genoa-X。

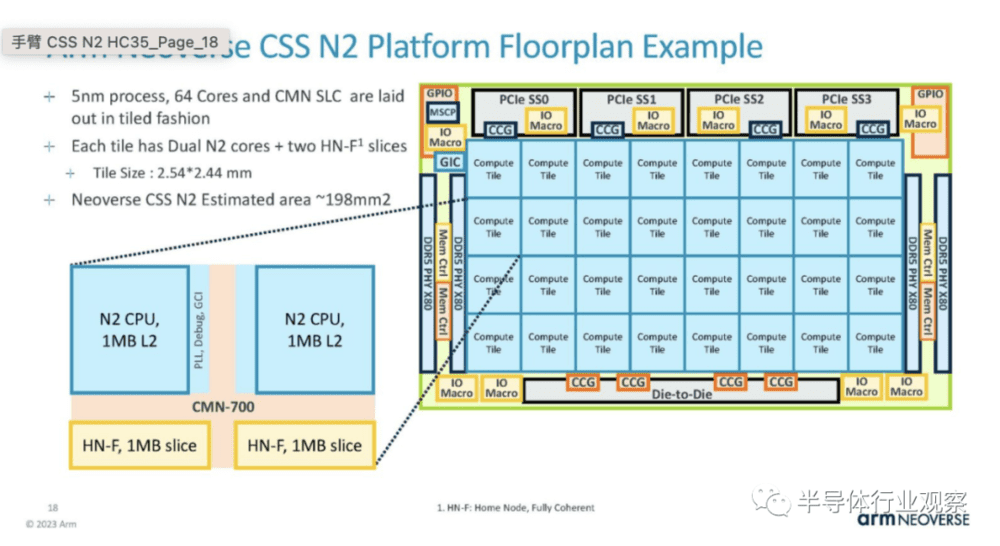

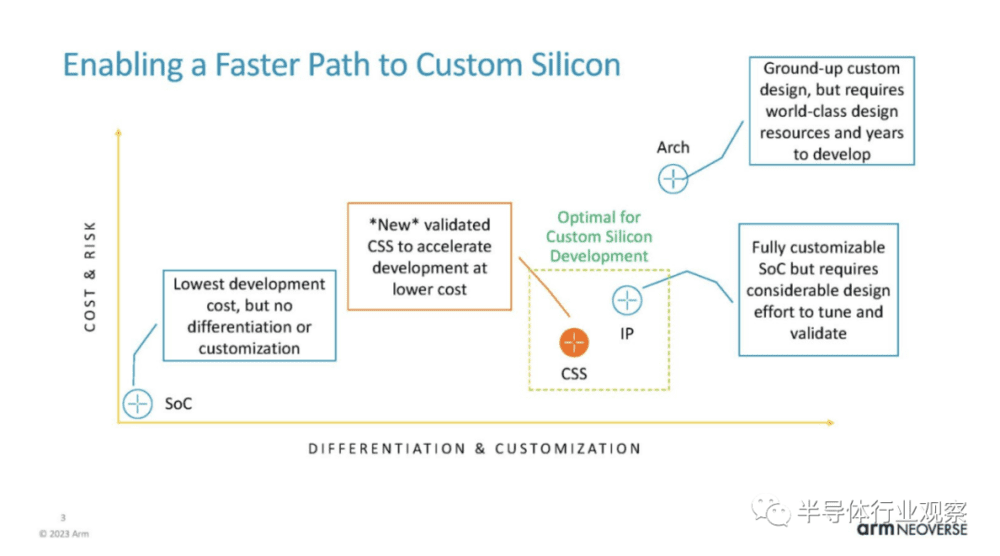

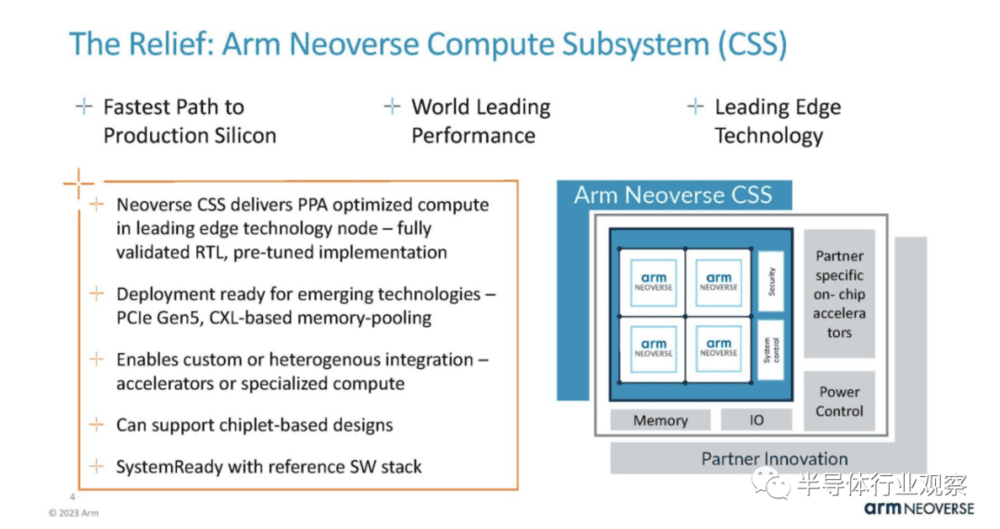

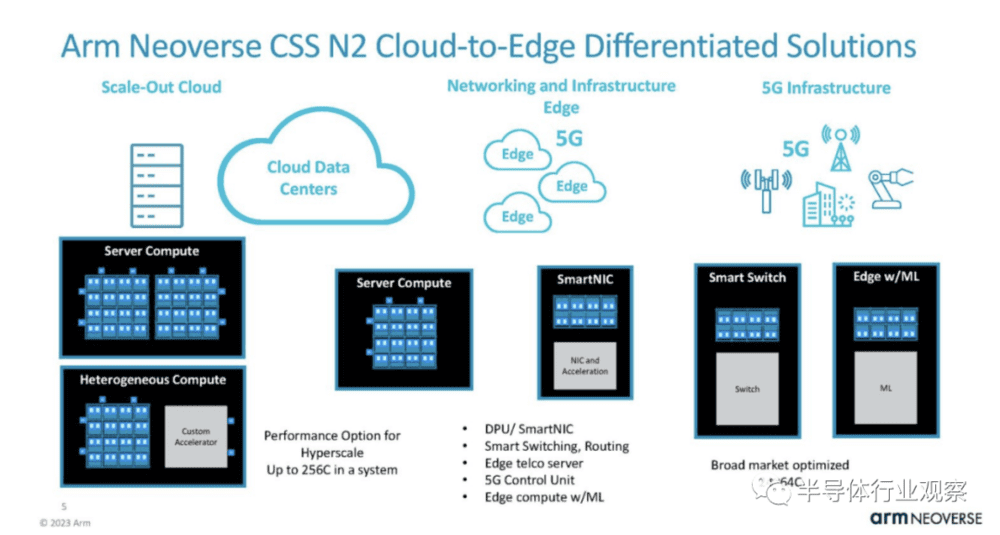

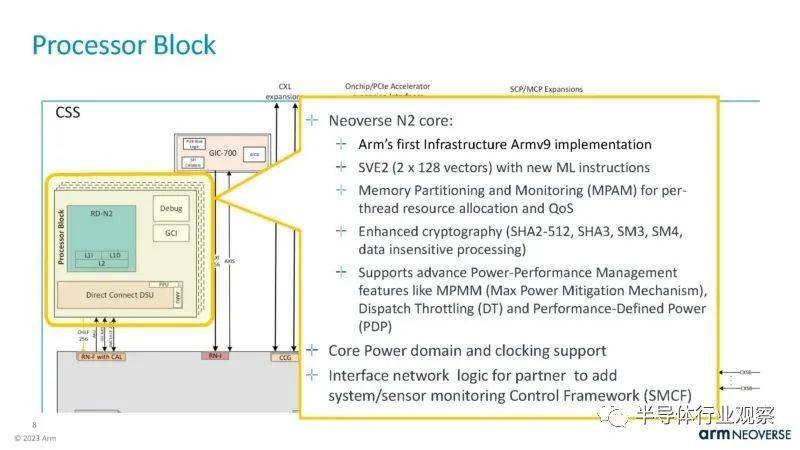

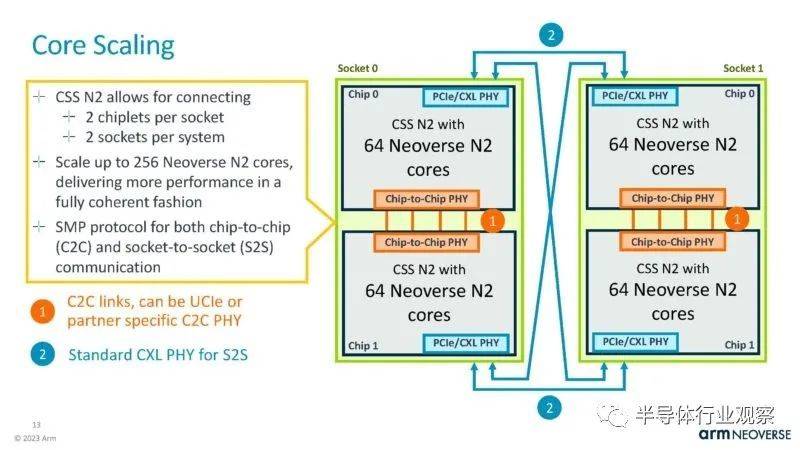

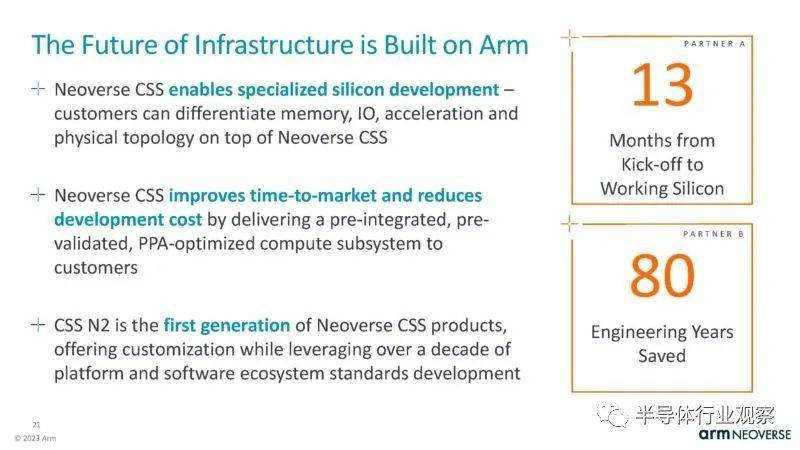

在 Hot Chips 2023 上,Arm 展示了一种实现Neoverse N2 内核的新方法。Arm Neoverse 计算子系统或 Neoverse CSS ,该系统不仅仅授权 N2 核心 IP,还允许客户购买更大的 IP 模块以投入设计。

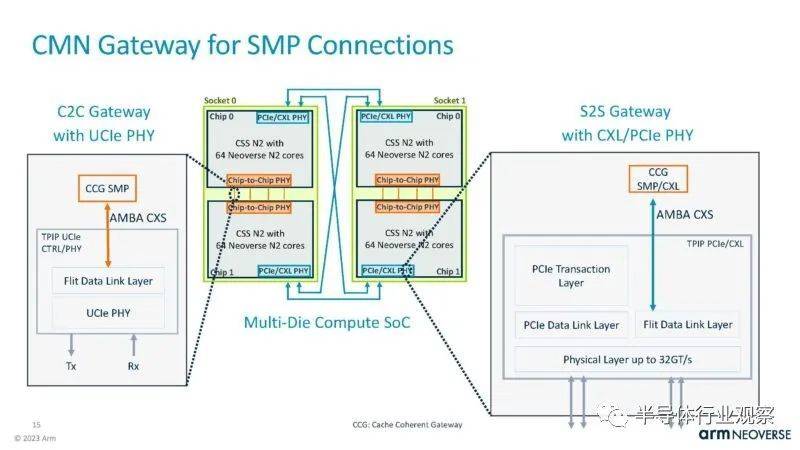

Arm 的目标是 Neoverse CSS,让 Chiplet 社区能够更轻松地集成 Noeverse N2 内核。

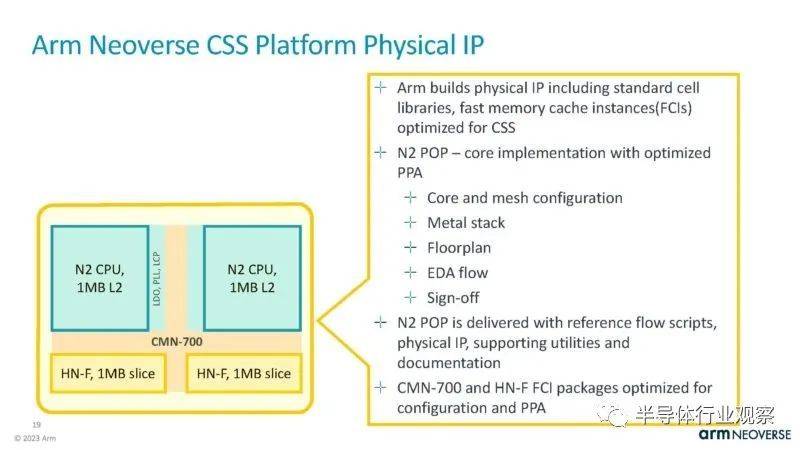

借助新的经过验证的 CSS 解决方案,实现 Arm 内核所需的工作量更少,从而加快了开发速度,但 Arm 还有其他选择。

Neoverse CSS 已完全验证 RTL 调整并准备好实施到设计中。

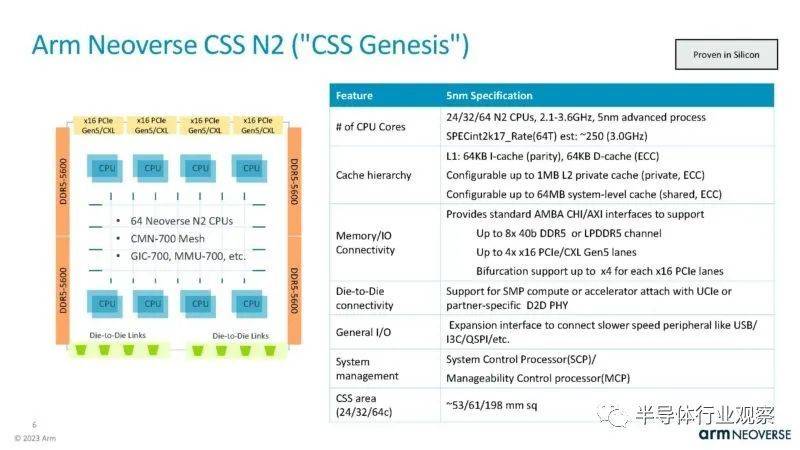

第一个 Neoverse CSS 产品是 Neoverse CSS N2。它使用 Arm 的横向扩展 Neoverse N2 内核,并允许公司选择内核集群并在设计中实现它们。

N2 可从每芯片 24、32 和 64 个核心设计进行扩展。它具有连接 DDR5、LPDDR5、PCIe/CXL 和其他类型 IP 的接口。

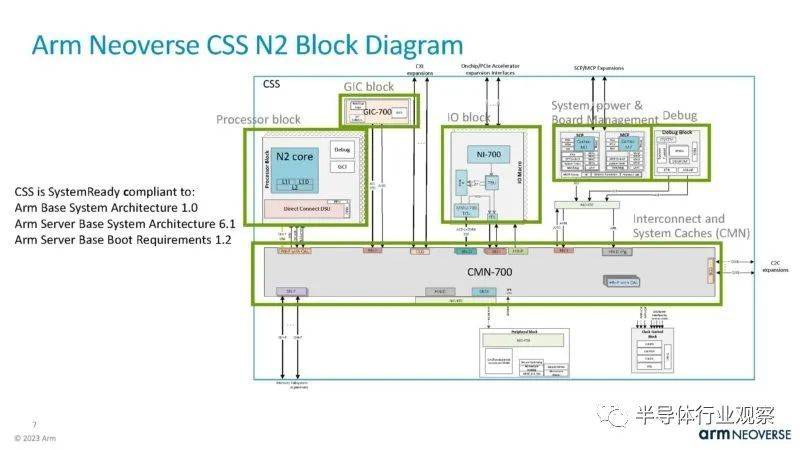

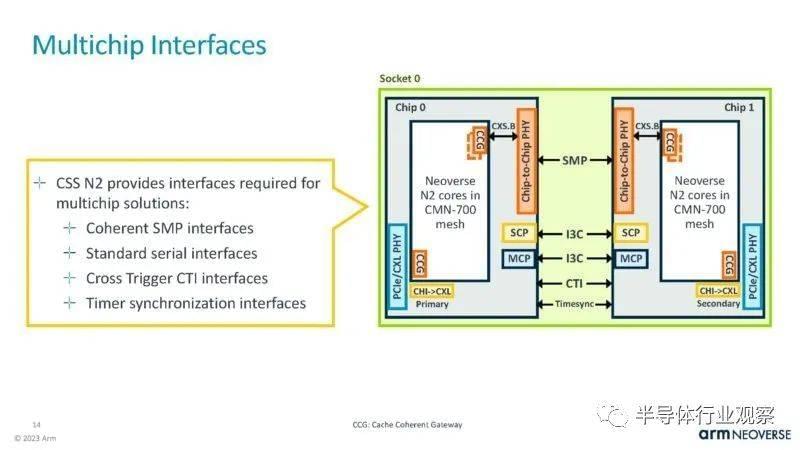

这是框图。Arm 在这里使用 CMN-700 将不同的组件连接在一起。CSS 开箱即用,符合 Arm 标准,这是有道理的。

处理器 IP 模块基于 Neoverse N2 内核。

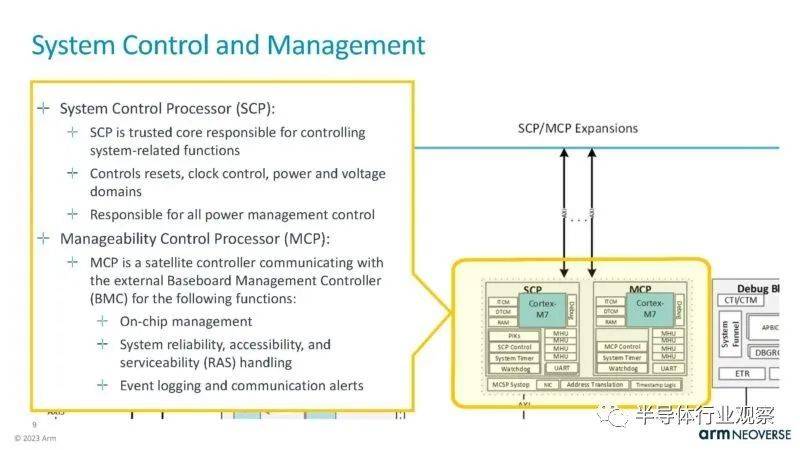

还有一个用于系统控制和管理的IP块。

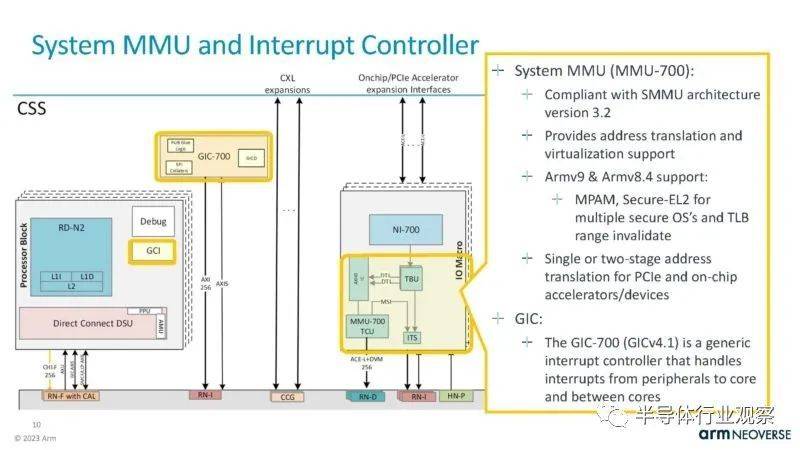

还有一个系统MMU和中断控制器。

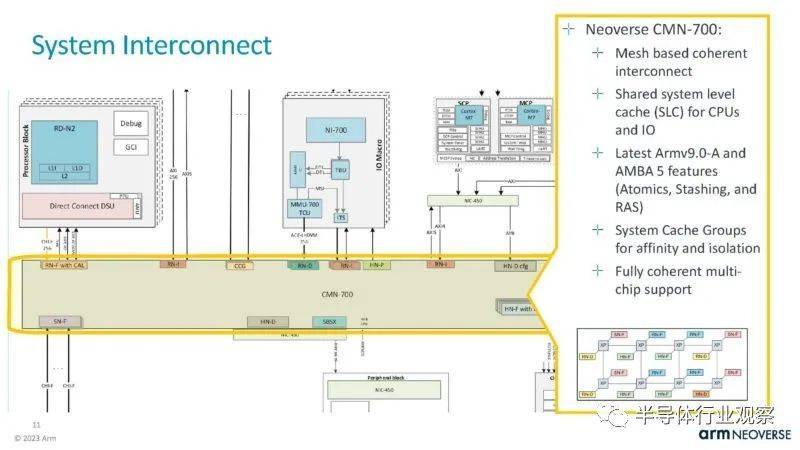

同样,Neoverse CMN-700 包含系统级缓存和基于网格的一致互连。

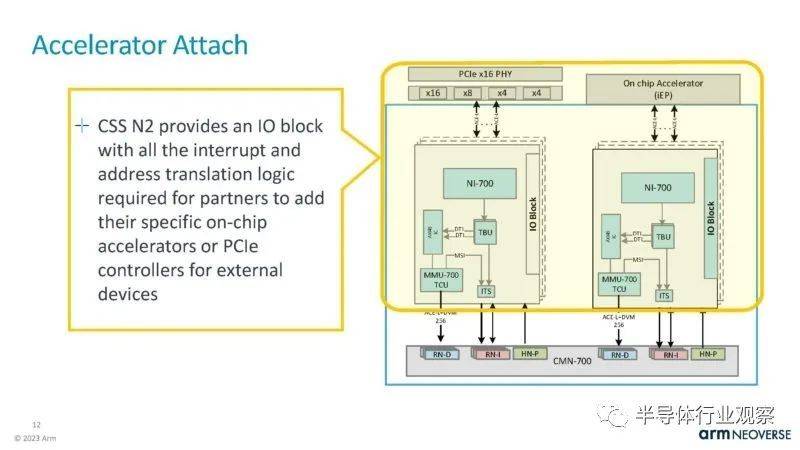

Arm 的目标客户是想要附加加速器的供应商,因此它拥有用于连接这些加速器的 IP。

通过将两个 64 核 Neoverse N2 小芯片连接在一起,Arm 可以达到每个插槽 128 个核心。这告诉我们,Arm 的目标并不是成为这一代具有竞争力的高密度服务器 CPU 基础。根据我们迄今为止所看到的Marvell Octeon 10等部件和Ampere Altra Max M128-30等 Neoverse N1 128 核心部件, 28 个 Arm Neoverse N2 核心将无法与 AMD 发货的 Bergamo 性能相匹配。这确实适合那些需要 CPU 内核作为加速器的人。

芯片和小芯片有不同的接口选项。

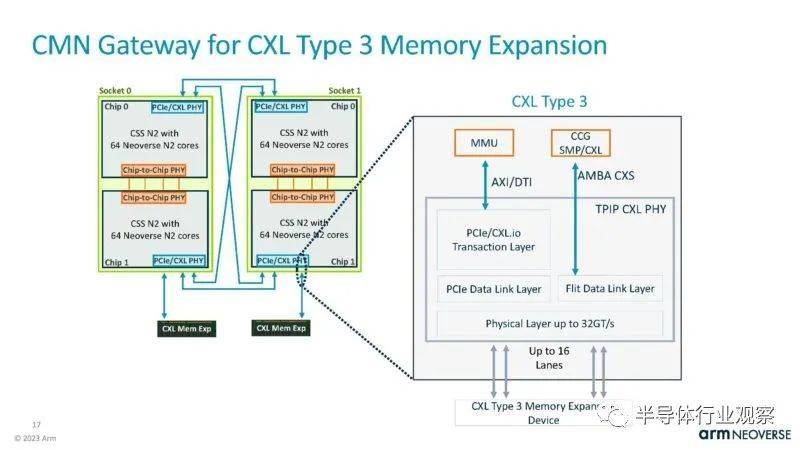

这是 CMN 网关,但同样,这似乎并不是为高端多插槽 CPU 系统设计的。

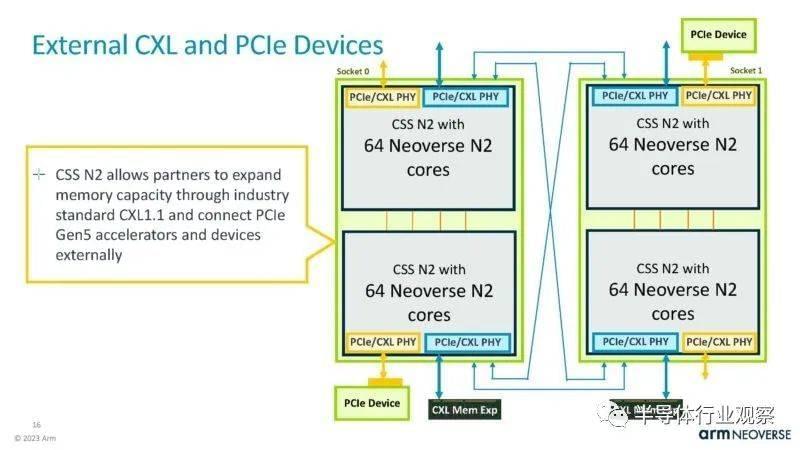

这是添加的有关 CXL 和 PCIe IP 的幻灯片。

Arm 表示,通过正确添加的 IP,它可以支持CXL Type-3 内存扩展设备。

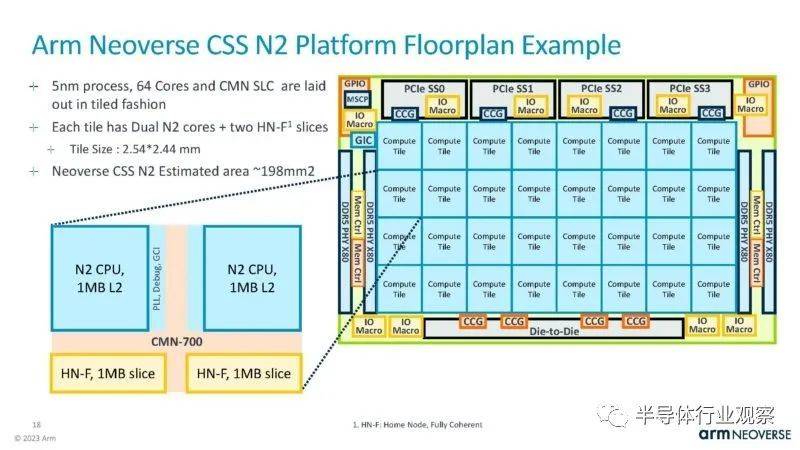

以下是以 32 核设计的 Arm Neoverse CSS N2 布局为例。

在这里,我们可以有两个 N2 块,并通过 CMN-700 连接所有内容。

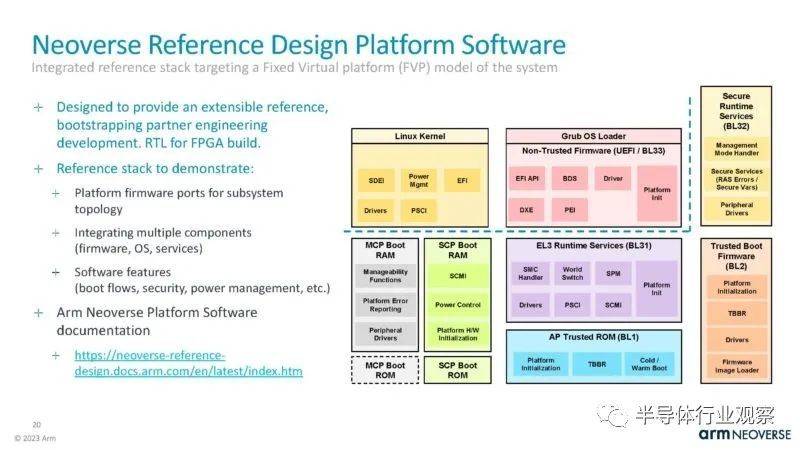

除了布局规划外,Neoverse CSS 还拥有 RTL 和其他软件和设计平台工具,以帮助加快开发速度。

Arm 表示,利用这一点,它可能能够将设计速度加快几个季度。

英特尔和 AMD 需要解决这个问题。随着时间的推移,Arm 的嵌入式 Neoverse CSS 可能会扩展到其他核心类型。未来,下一个问题是这与小芯片 CPU 的相关性如何。例如,如果英特尔允许代工客户购买并集成 E-core 小芯片,那么下一步就是让希望构建封装的公司变得更容易。尽管如此,Arm 今天已经推出了 CSS,理论上,它允许公司轻松地将 N2 内核与加速器集成到非基于小芯片的 SoC 中。

这是一个很酷的解决方案,我们希望能够扩展。另一方面,人们也可能会争辩说,Arm 可以在未来为生态系统销售预制的、可随时与 UCIe 集成的 Neoverse 芯片。

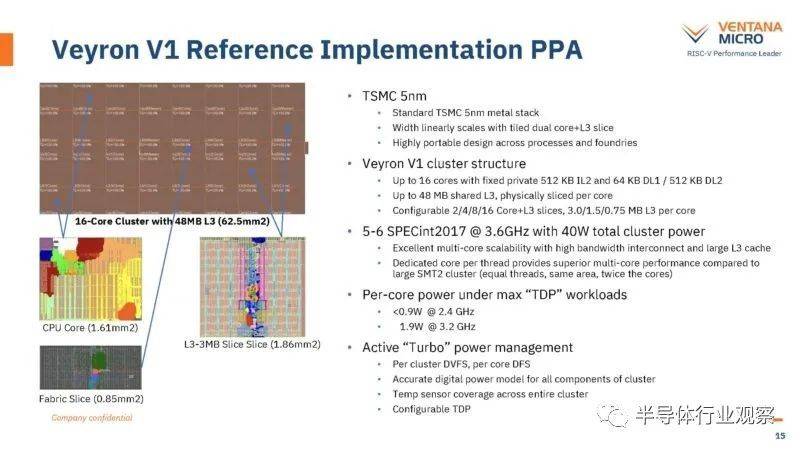

Ventana 的RISC-V芯片Veyron V1

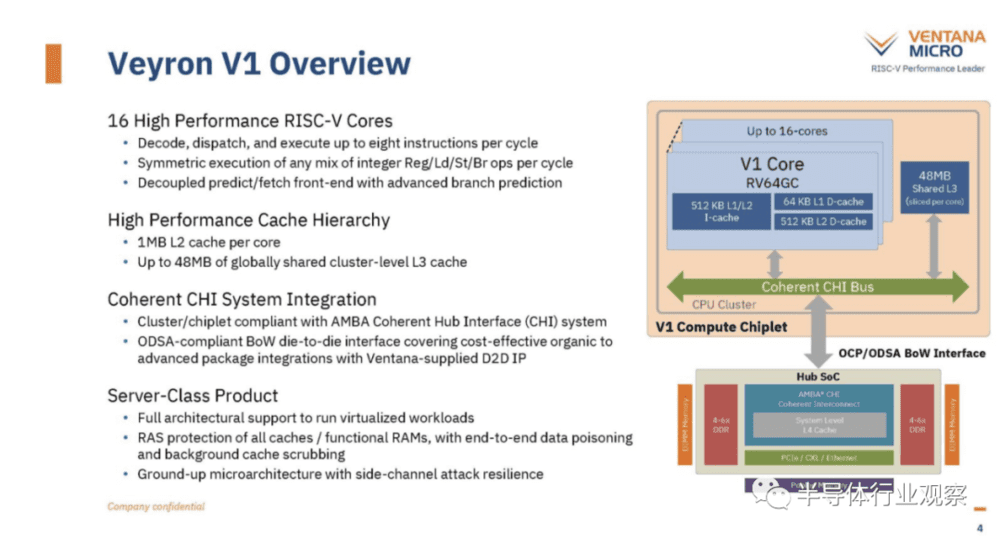

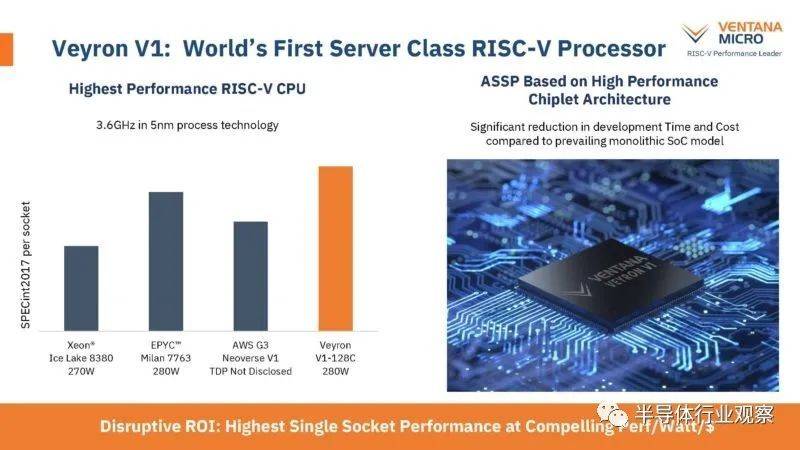

在 Hot Chips 2023 上,RISC-V CPU 初创公司 Ventana Micro 展示了其新数据中心 Veyron V1。Ventana Veyron V1 着眼于数据中心 RISC-V CPU 的新时代。虽然这是在 V1 产品上,但该公司显然已经在使用 V2 产品了。

Ventana 为Veyron V1 提供了一个有趣的目标市场,最好的描述是“只要我们能找到需求”。

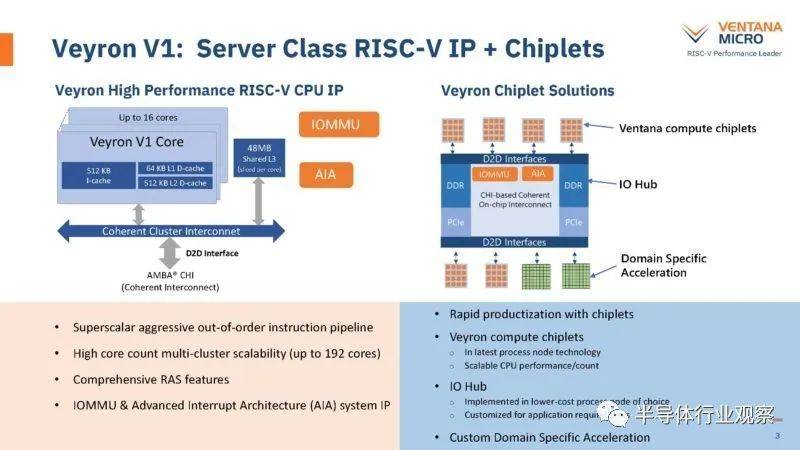

之所以有这个想法,是因为Ventana Micro 拥有一个 RISC-V CPU 内核,每个小芯片最多有 16 个内核,然后将它们与具有 DDR 内存控制器和 PCIe 等功能的 I/O 集线器结合起来。Ventana 表示,它可以将 Veyron V1 扩展至 192 个核心,但它也可以集成特定领域的加速器。

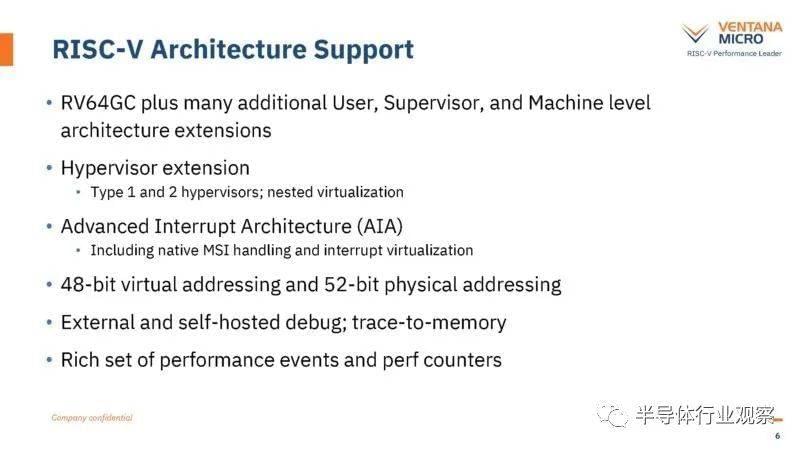

以下是芯片的关键规格,包括核心、缓存等。Ventana 表示,Veyron V1 将支持虚拟化等功能,并采取措施使其更能抵御侧信道攻击。在支持方面,令我们惊讶的是该公司已经在讨论嵌套虚拟化。我们看到的 Arm Neoverse N1 芯片甚至不支持嵌套虚拟化。

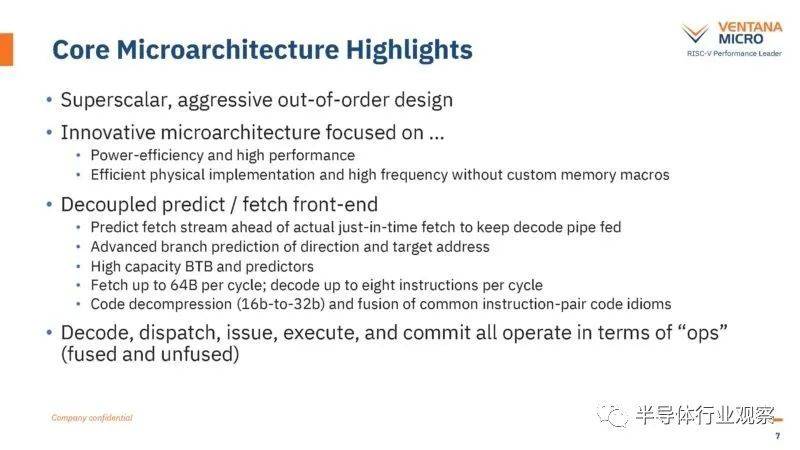

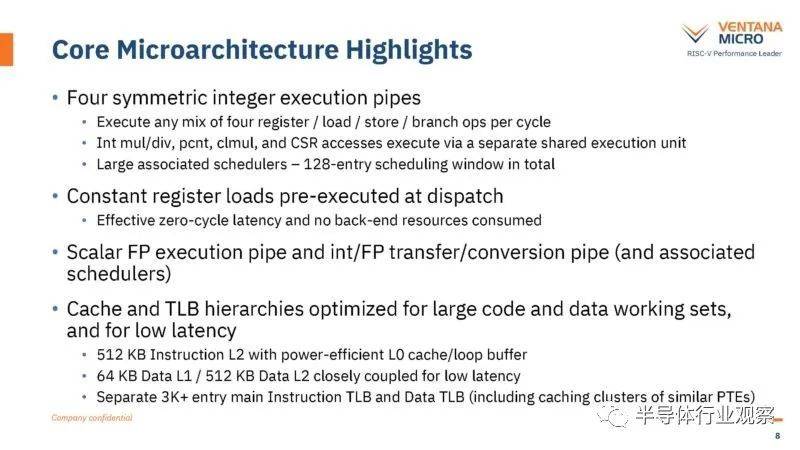

这里有更多关于核心微架构的信息。

这里有更多关于这一点的内容。

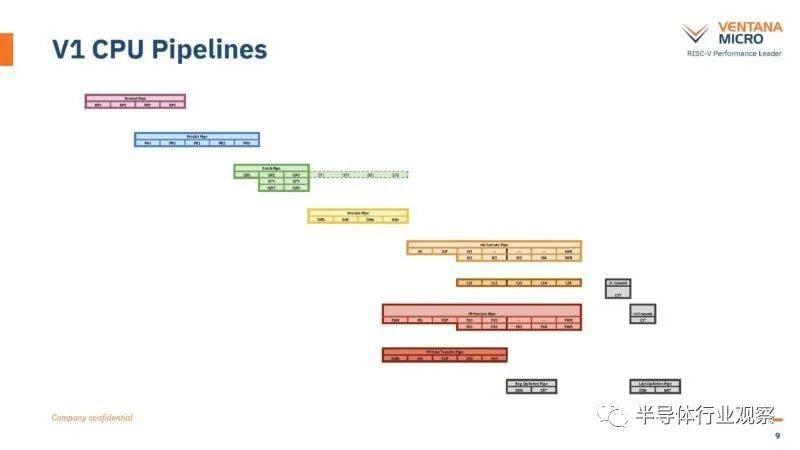

这是一个非常难以阅读的图表中的管道。

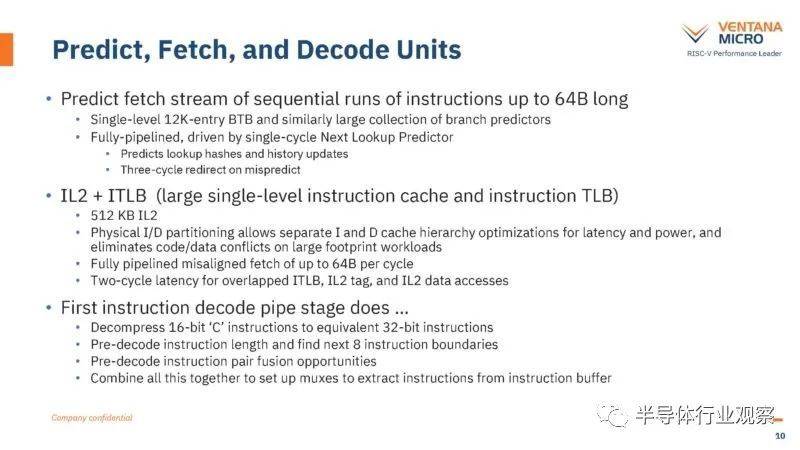

这是预测、获取和解码幻灯片:

以下是加载/存储详细信息:

从处理器集群规模来看,每个16核集群拥有高达48MB的L3缓存。

如果该公司将 UCIe 纳入此处只是为了说它是首批UCIe CPU之一并倾向于小芯片,那就真的很有趣了。

在性能方面,Ventana 的目标是达到上一代 128 核 Veyron的性能。AMD EPYC Bergamo等 CPU 的数量比 Milan 高得多(>2 倍)。该公司表示,V2 尚未投入生产,而Bergamo已经普遍上市。

在 RISC-V 市场中,Ventana 目前不必比 AMD 和 Intel 更快。它只需不是 x86,不是 Arm,而是 RISC-V。人们正在将 RISC-V 专门视为未来 CPU 和 xPU 设计中 Arm 的替代品。

Ventana 还具有可用于 TSMC 5nm的参考 Veyron V1 实现。

RISC-V 是 x86 替代领域值得关注的技术。Arm 已经很大了,但随着它致力于改进其业务,RISC-V 有机会颠覆 Arm 所做的大量工作。2016年,当我们评测Cavium ThunderX时,Arm服务器CPU非常粗糙。从那时起,从单一 x86 架构代码库和基础设施迁移到 x86 和 Arm 的多架构世界已经做了很多工作。RISC-V 正在利用其中的大量工作来提高其市场速度。它的 I/O 芯片设计似乎也借鉴了 AMD 的经验教训,这已被证明是成功的。

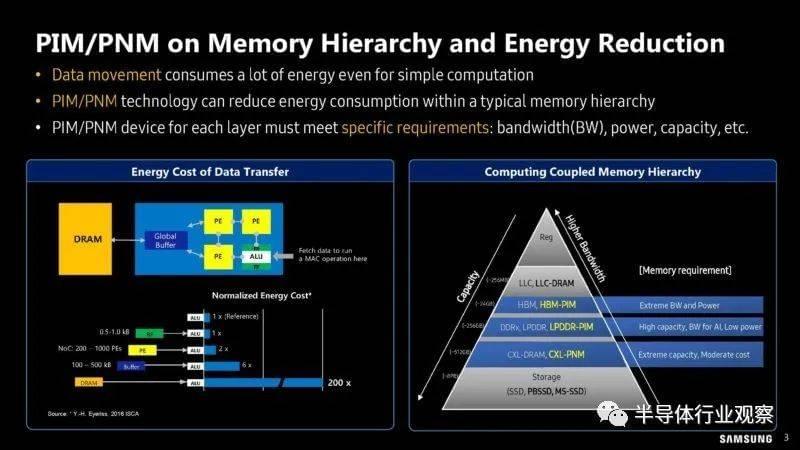

三星展示PIM内存技术

在 Hot Chips 2023上,三星再次谈论其内存处理(PIM),并进行了新的研究和新的转变。如三星所说,计算中最大的成本之一是将数据从不同的存储和内存位置移动到实际的计算引擎。

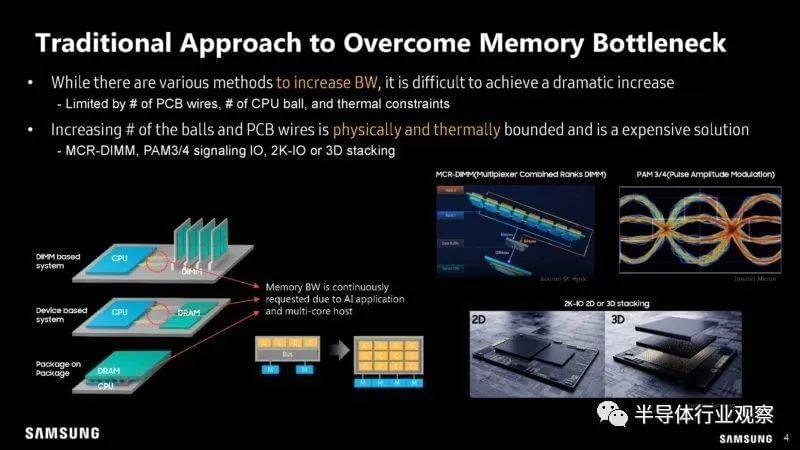

目前,公司尝试为不同类型的内存添加更多通道或通道,但这有其局限性。

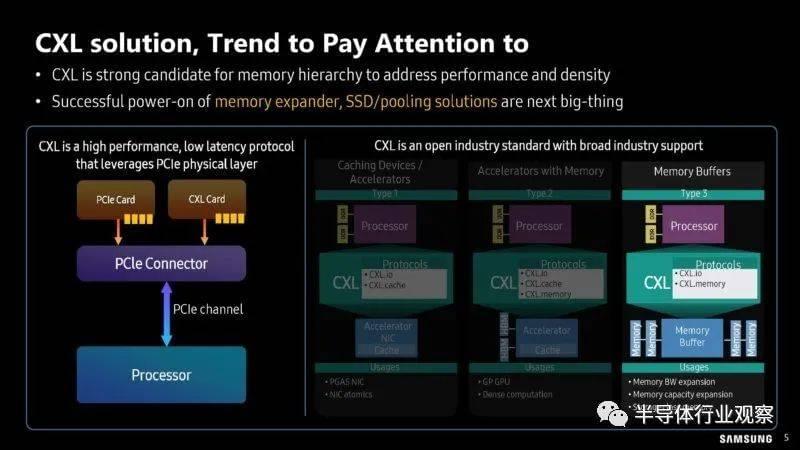

三星正在讨论 CXL。CXL 很有帮助,因为它允许重新调整 PCIe 线路的用途,以提供更多内存带宽。

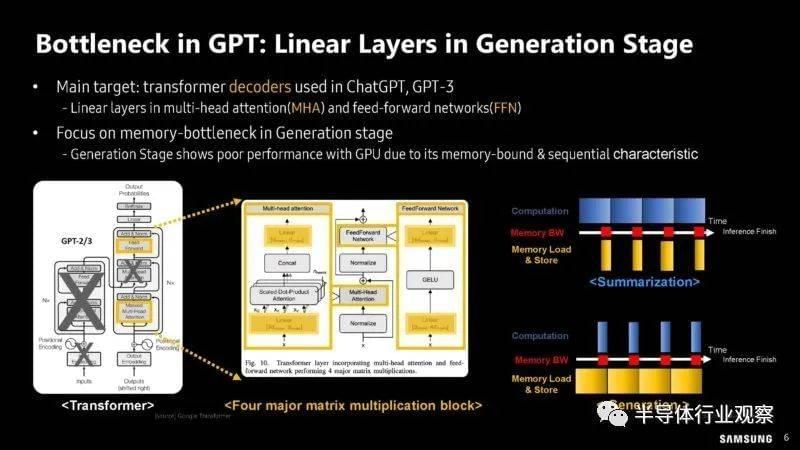

在三星的分享中,他们也谈到了ChatGPT的瓶颈。

三星同时也对 GPT 的计算溢出和内存限制工作负载进行了分析。

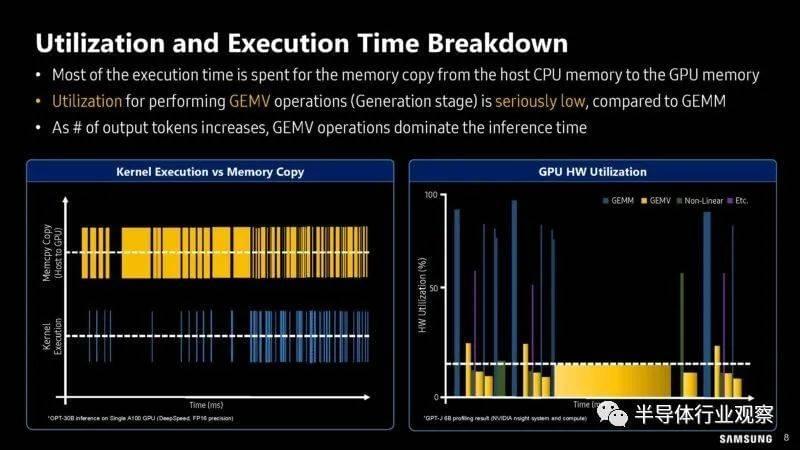

以下是关于利用率和执行时间方面的分析工作的更多信息。

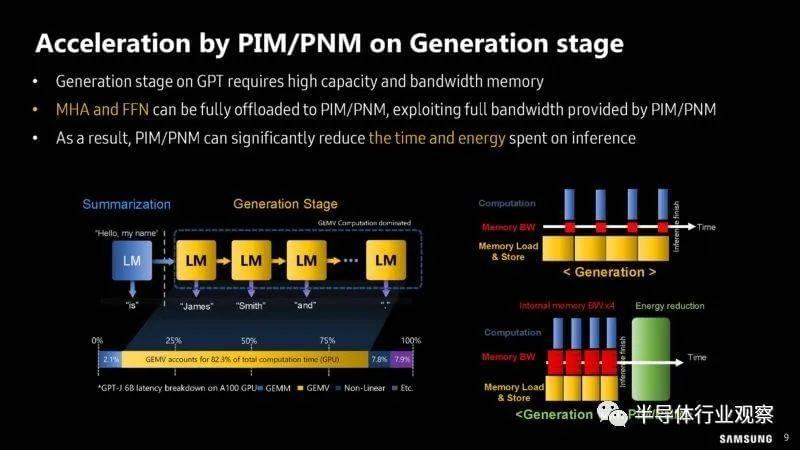

三星展示了如何将部分计算管道卸载到内存处理(PIM)模块。

在内存模块而不是加速器上进行处理可以节省数据移动,从而降低功耗和互连成本。

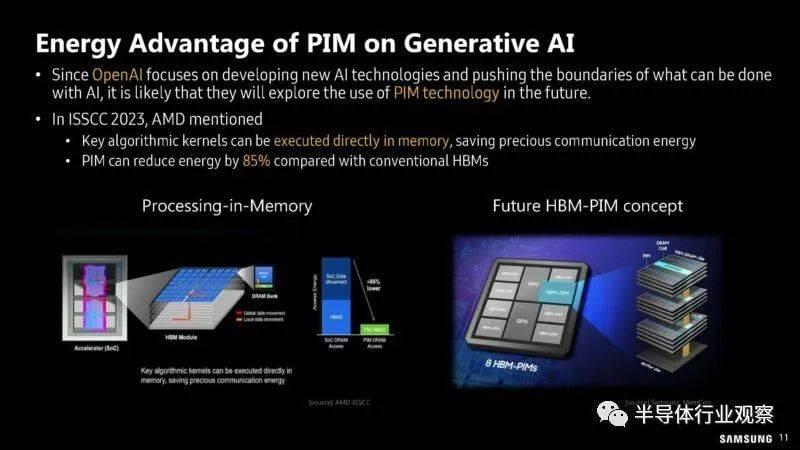

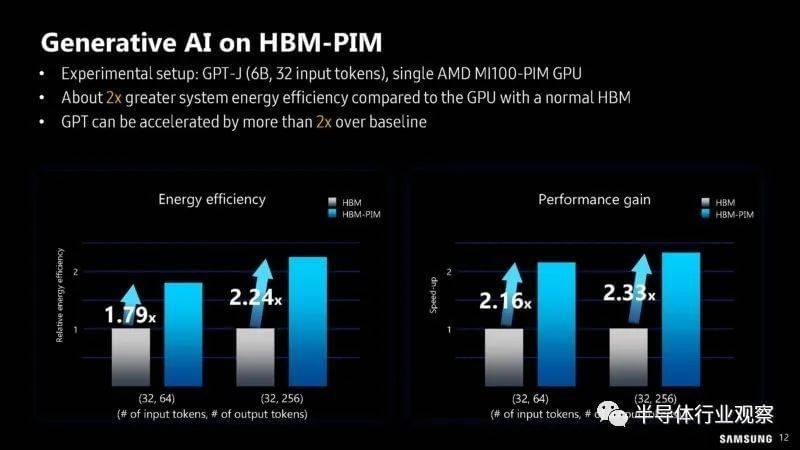

在 SK 海力士谈论其解决方案中的 GDDR6 时,三星则展示了其高带宽内存 HBM-PIM。

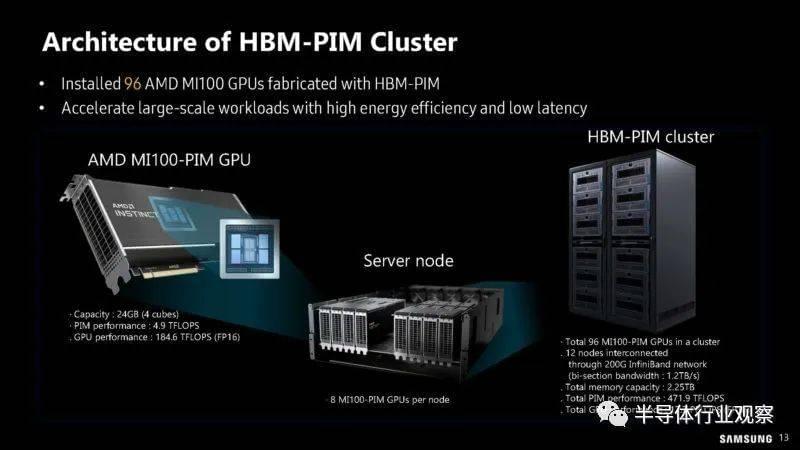

显然,三星和 AMD 的 MI100 带有 HBM-PIM 而不仅仅是标准 PIM,因此它可以构建一个集群,这样它就可以拥有听起来像 12 节点 8 加速器的集群来尝试新内存。

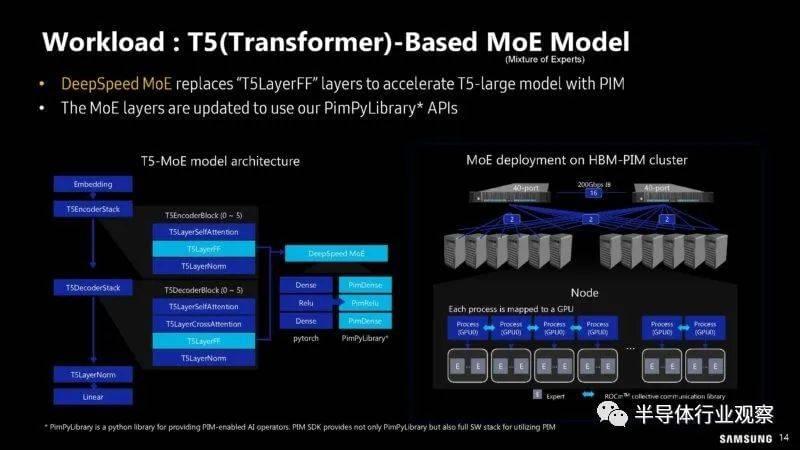

以下是 T5-MoE 模型如何在集群中使用 HBM-PIM。

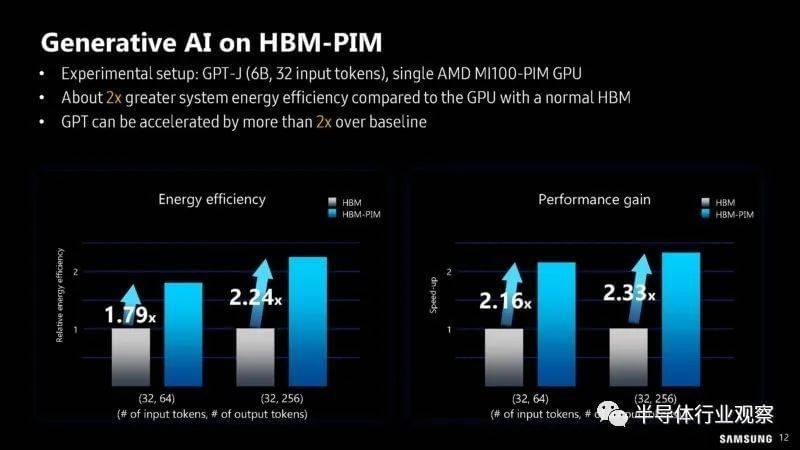

以下是性能和能源效率的提升。

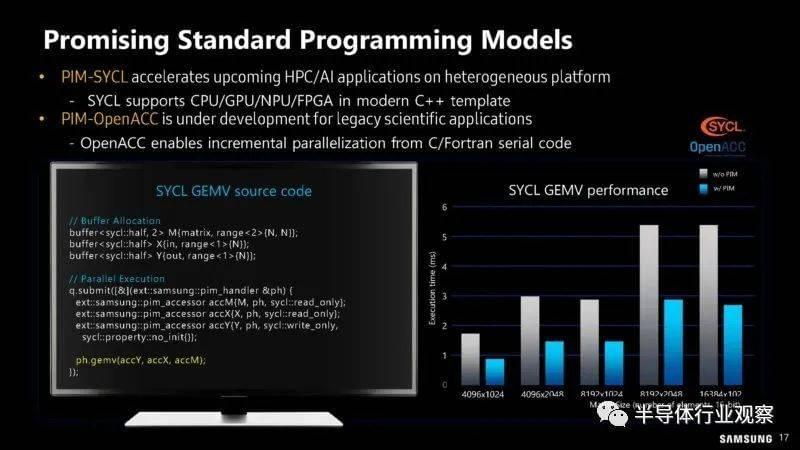

其中很大一部分还在于如何让 PIM 模块做有用的工作。这需要软件来编程和利用 PIM 模块。

三星希望能够将此内置于标准编程模块中。

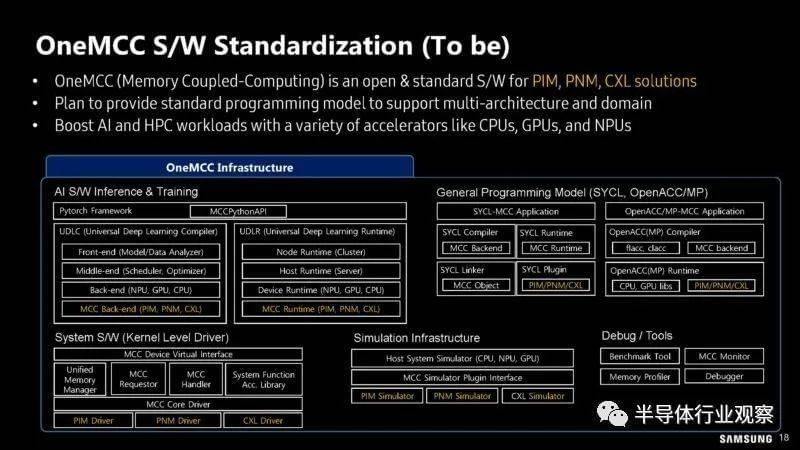

这是用于内存耦合计算的 OneMCC 的未来状态,但这听起来像是未来的状态,而不是当前的状态。

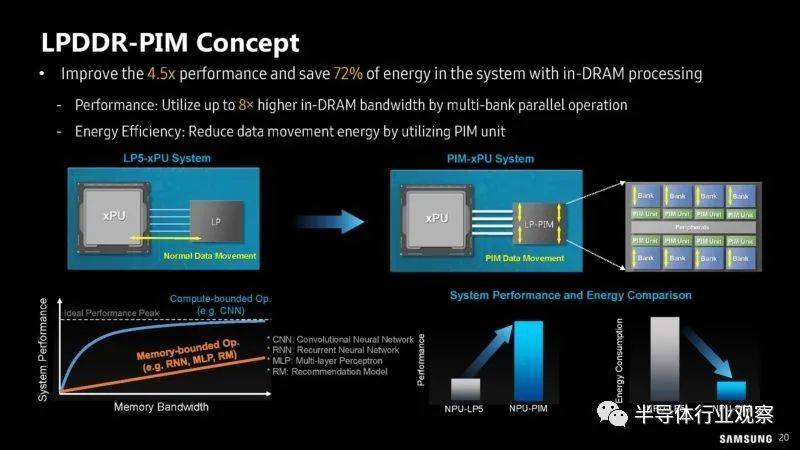

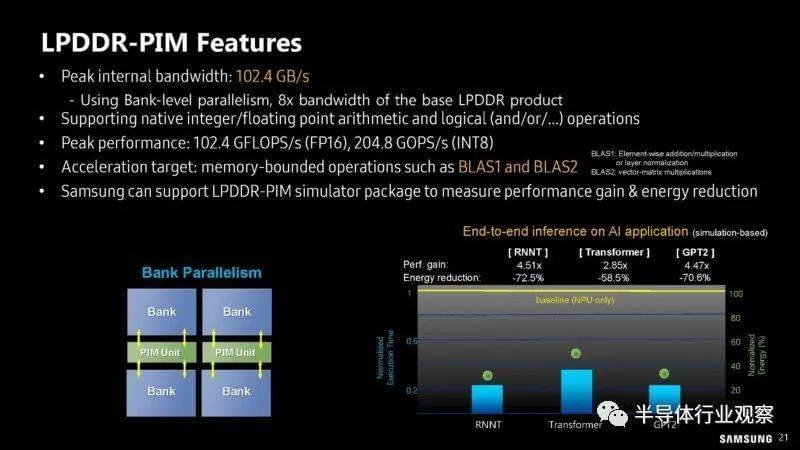

看来三星不仅展示了 HBM-PIM,还展示了 LPDDR-PIM。与当今的一切一样,它需要一个生成式人工智能标签。

这似乎更像是一个概念,而不是集群中 AMD MI100 上使用的 HBM-PIM。

该 LPDDR-PIM 的内部带宽仅为 102.4GB/s,但其想法是,将计算保持在内存模块上意味着无需将数据传输回 CPU 或 xPU,从而降低功耗。

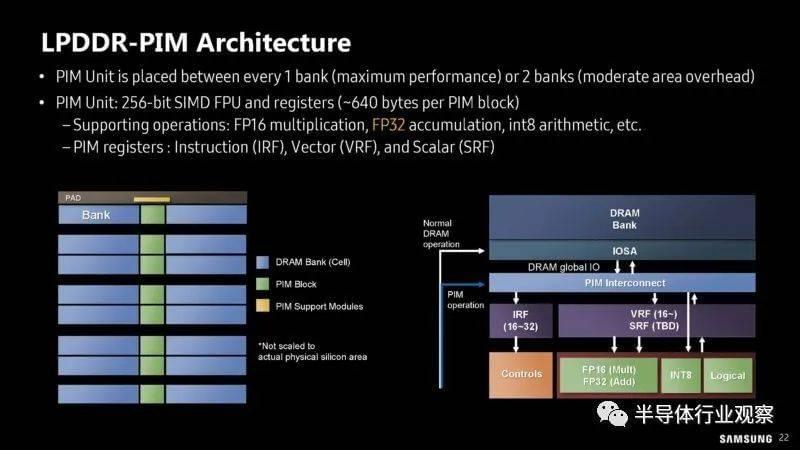

以下是模块上包含 PIM 组和 DRAM 组的架构。

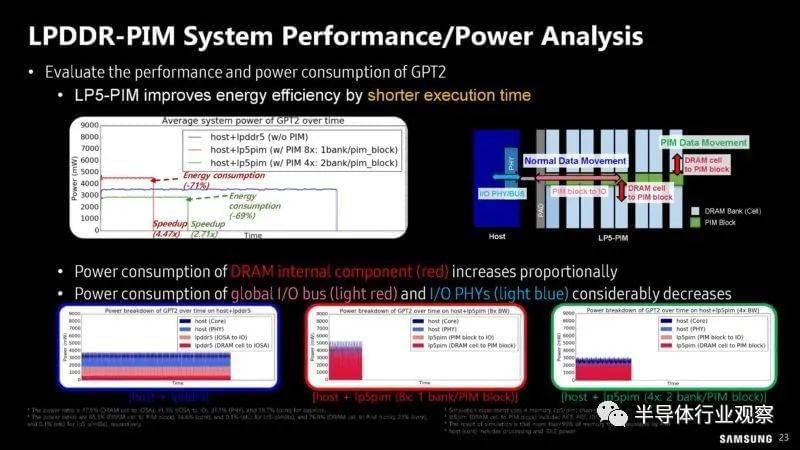

以下是可能的 LP5-PIM 模块的性能和功耗分析。

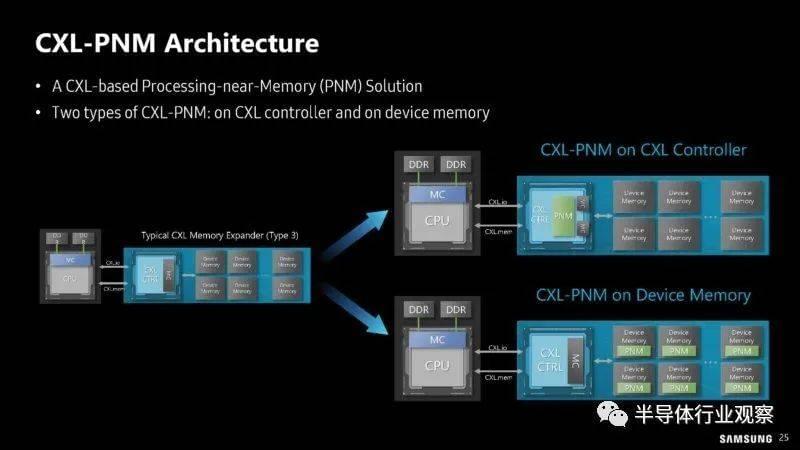

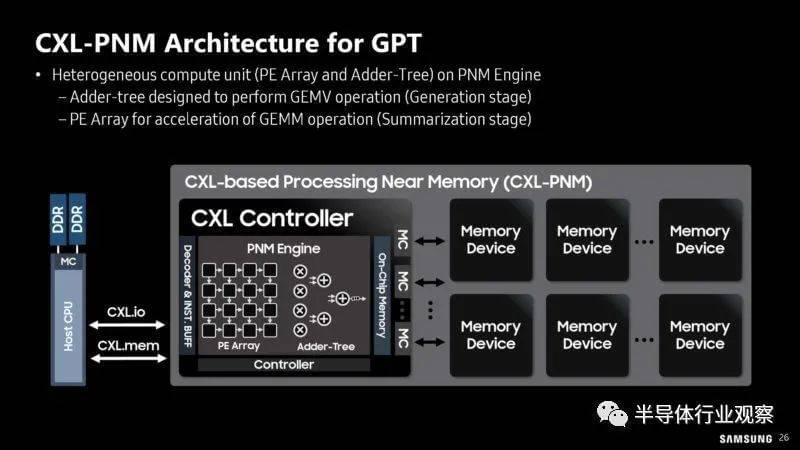

如果 HBM-PIM 和 LPDDR-PIM 还不够,三星正在考虑将计算放到 PNM-CXL 中的 CXL 模块上。

这里的想法不仅仅是将内存放在 CXL Type-3 模块上。相反,三星建议将计算放在 CXL 模块上。这可以通过向 CXL 模块添加计算元件并使用标准内存或在模块上使用 PIM 和更标准的 CXL 控制器来完成。

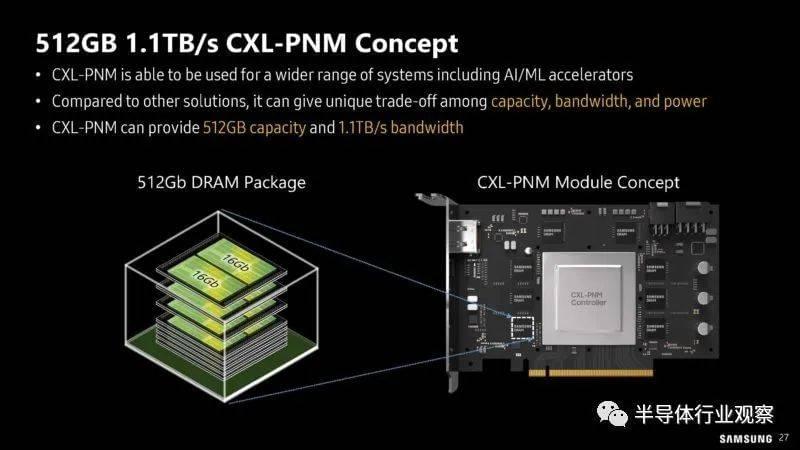

当然,我们已经展示了这如何帮助 GPT 方面的生成人工智能。三星也推出了一款概念 512GB CXL-PNM 卡,带宽高达 1.1TB/s。

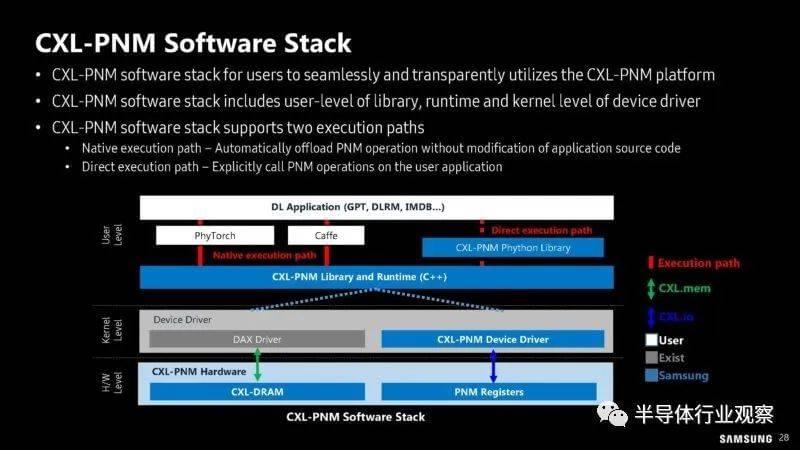

这是三星提出的 CXL-PNM 软件堆栈。

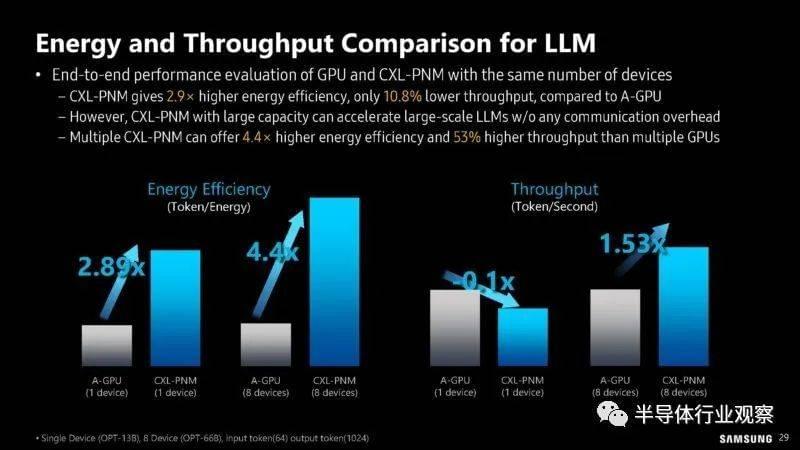

以下是大规模 LLM 工作负载的预期节能和吞吐量。CXL 通常通过也用于 PCIe 的电线,因此传输数据的能源成本非常高。因此,能够避免数据传输会带来巨大的好处。

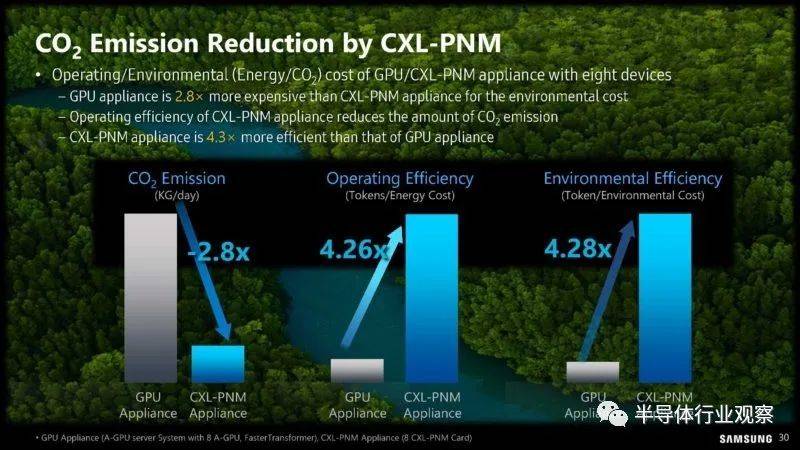

由于上述原因,三星也非常重视减排。

三星多年来一直在推动 PIM,但 PIM/PNM 似乎正在从纯粹的研究概念转变为真正希望将其产品化的公司。希望我们将来能看到更多这样的事情。CXL-PNM 最终可能成为此类计算的成熟领域。

SK 海力士的 AI 内存亮相

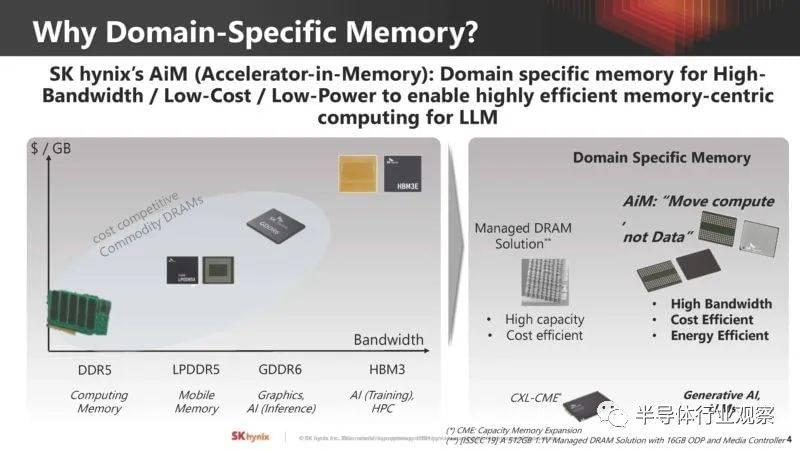

在 Hot Chips 2023上,SK 海力士将其在内存方面的专业知识应用于当今的大计算问题——人工智能。在展会上,它展示了其在具有特定域内存的内存中心计算方面的工作。该公司正在寻找方法来缓解当今人工智能计算面临的最大挑战之一,即与可用计算资源相关的内存容量和带宽。

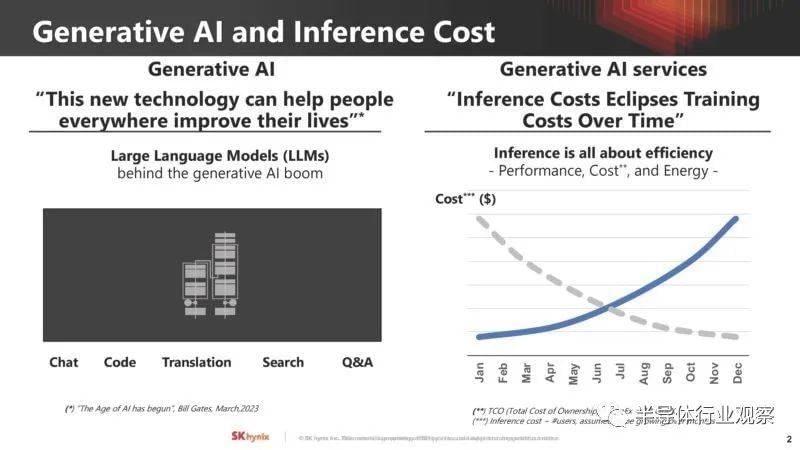

这是SK海力士的问题定义。生成式人工智能推理成本巨大。这不仅仅是人工智能计算。电源、互连和内存也导致了大量成本。

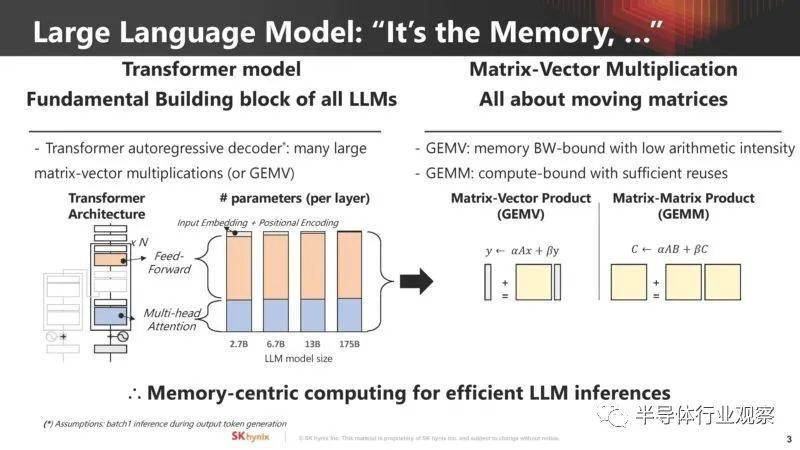

对于大型transformer模型,内存是一个主要挑战。这些模型需要大量数据,因此通常受到内存容量和带宽的限制。

SK 海力士认为,行业需要的不仅仅是内存,还需要不同类型的内存,包括内置计算功能的特定领域内存。三星和 SK 海力士一直致力于成为内存计算提供商,因为这是他们向价值链上游移动的方式。

在这一点上,我们将听到 Accelerator-in-Memory 或 SK hynix AiM。

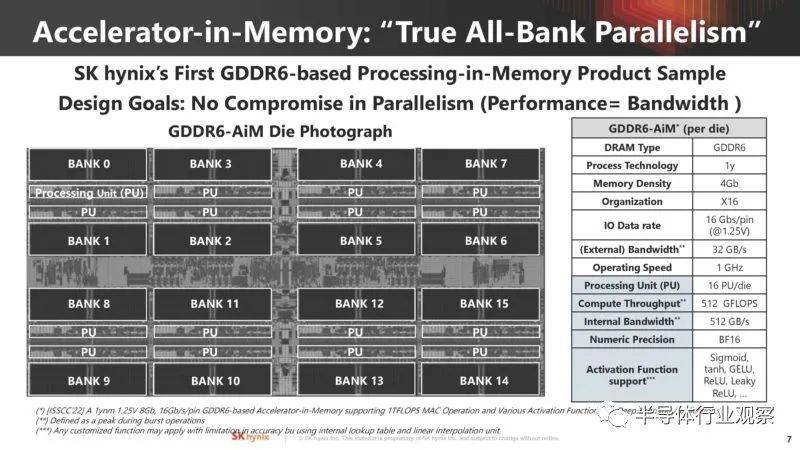

下面是 GDDR6 内存的外观,其中有多个内存组,每个内存组都有自己的 1GHz 处理单元,能够实现 512GB/s 的内部带宽。

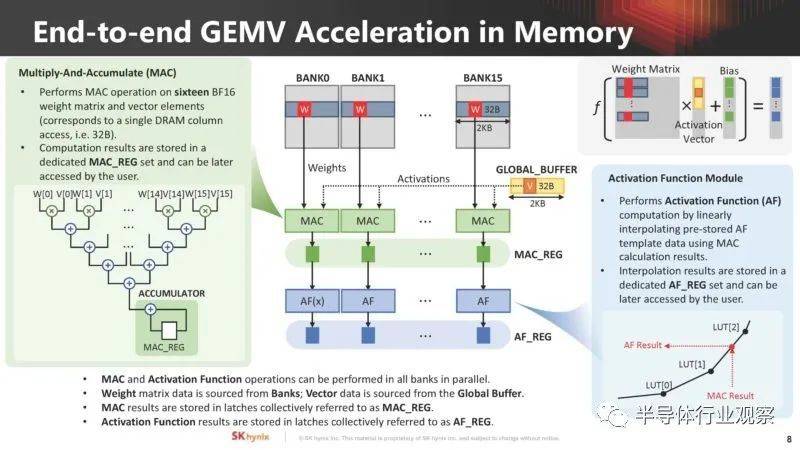

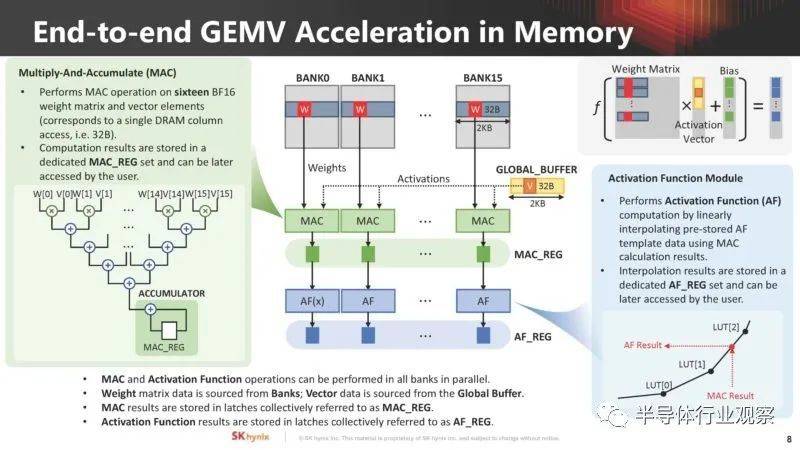

SK hynix 讨论了它计划如何在内存中进行 GEMV 以进行 AI 计算。权重矩阵数据来自bank,而矢量数据来自全局缓冲区。

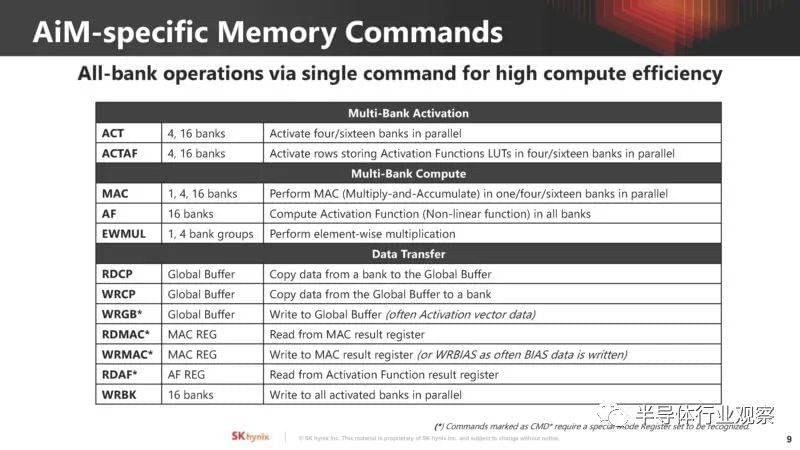

内存计算有特定的 AiM 内存命令。

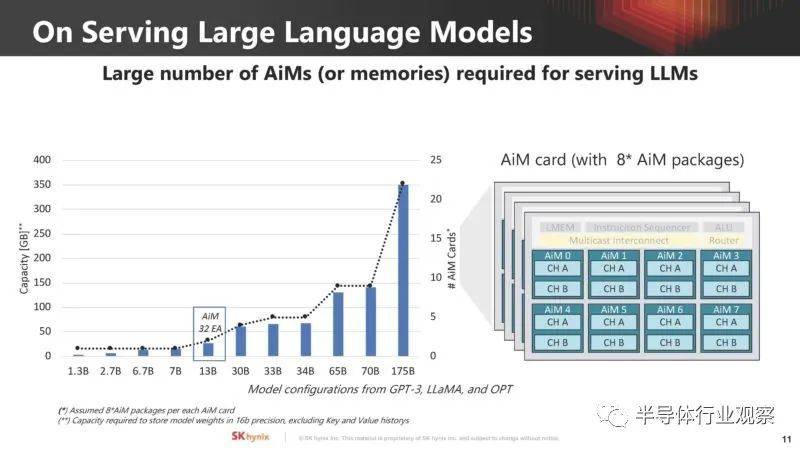

SK hynix 展示了大型语言模型所需的内存扩展方式以及 AiM 内存计算资源的需求。

以下是大型语言模型(LLM)的扩展方式:

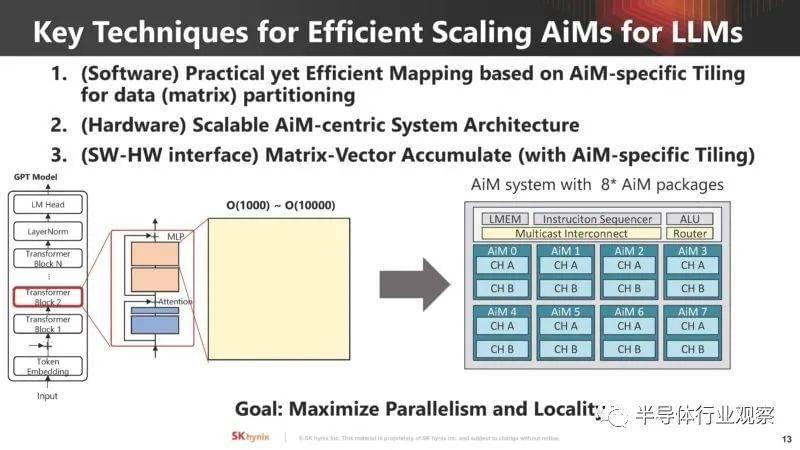

使用这种类型的 AiM 面临的一大挑战是它需要从软件端进行映射、为 AiM 构建硬件,然后需要一个接口。这是采用的其他重大障碍之一。

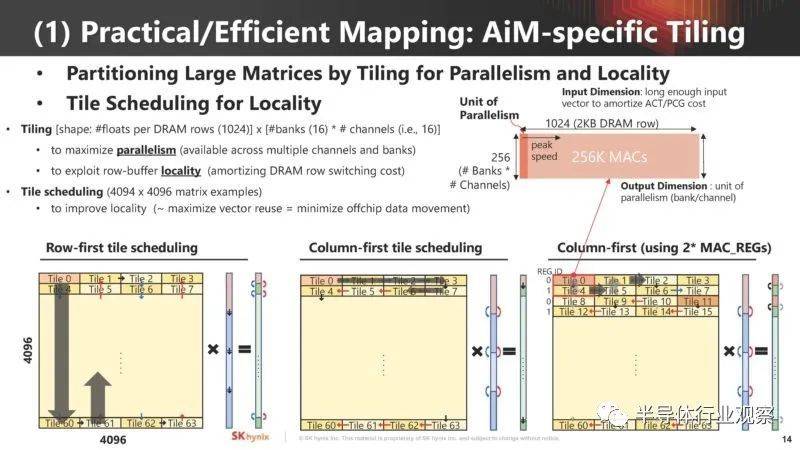

以下是 SK 海力士如何将问题映射到 AiM。

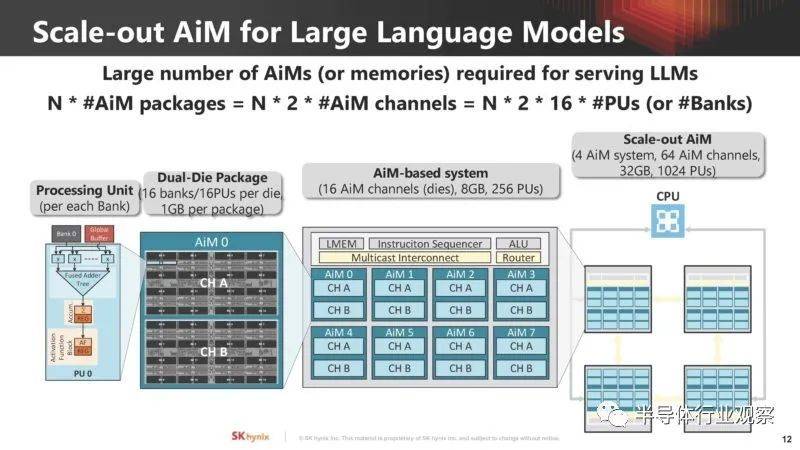

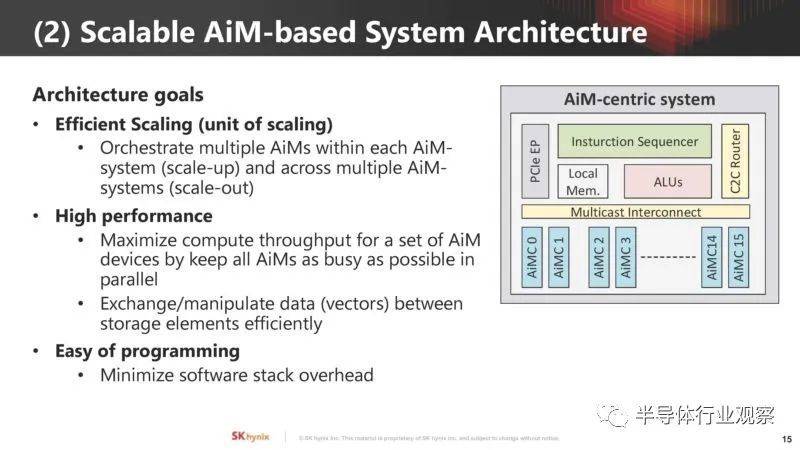

系统架构需要处理纵向扩展和横向扩展。

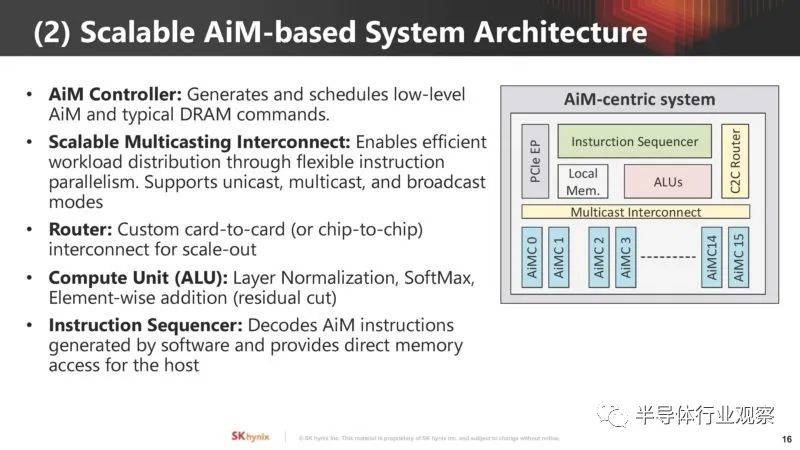

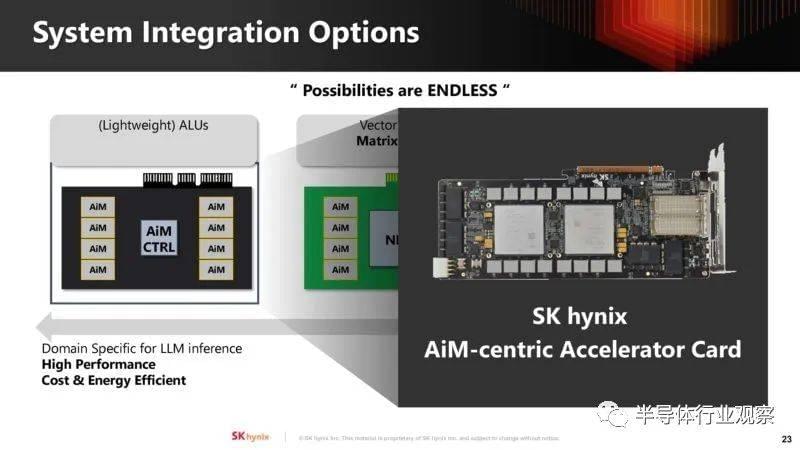

AIM 架构的关键组件包括 AiM 控制器、可扩展多播互连、路由器、计算单元 (ALU) 和指令排序器。

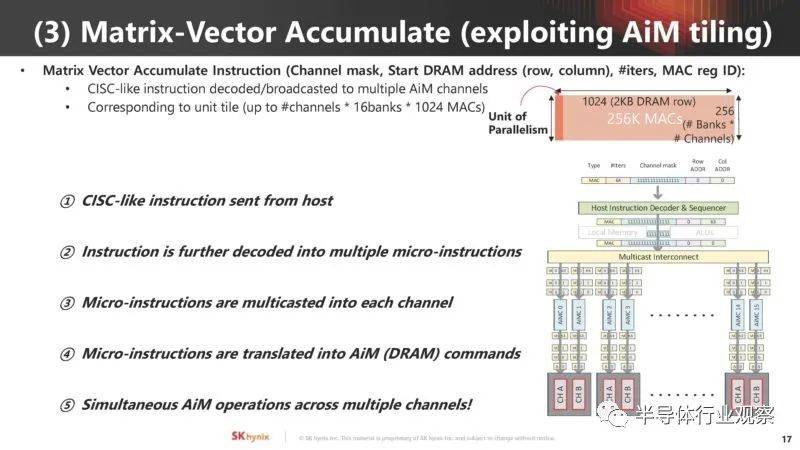

矩阵向量累加函数是 AI 工作负载的关键。SK hynix AiM 使用类似 CISC 的指令集来管理此操作。

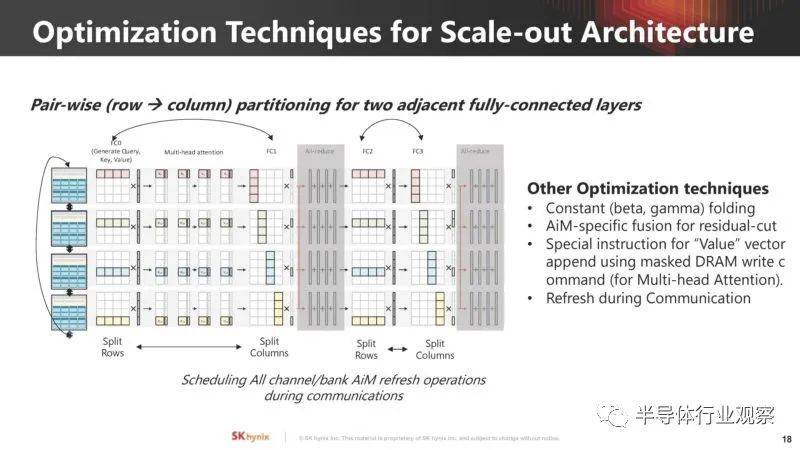

下一步是优化。对于新的架构,通常可以利用一些细微差别来获得更好的性能。

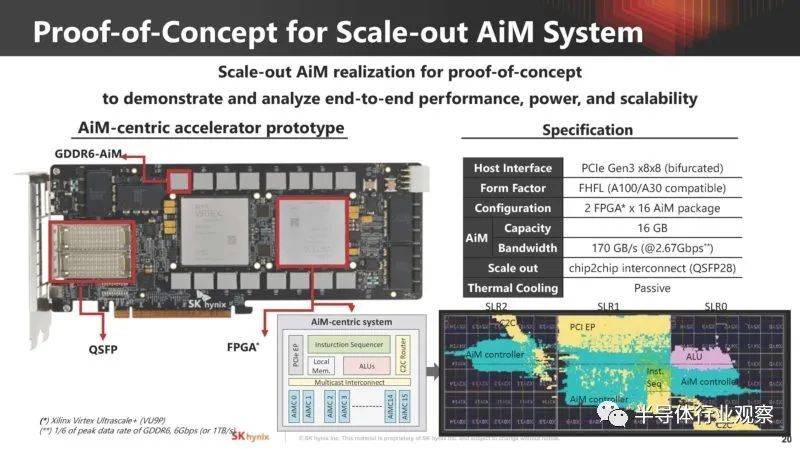

SK海力士并不只是抽象地谈论AiM。相反,它展示了使用两个 FPGA 的 GDDR6 AiM 解决方案的概念验证。

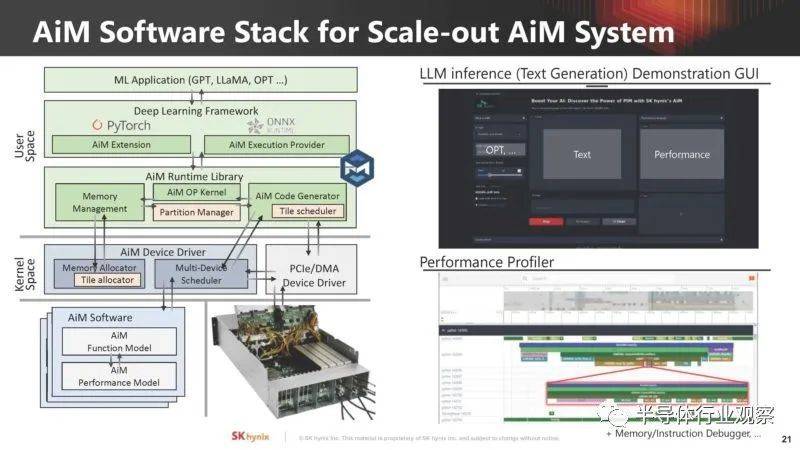

它还展示了 AiM 的软件堆栈。

听起来 SK 海力士并不打算出售这些卡,相反,这些卡似乎是用来证明这个概念的。

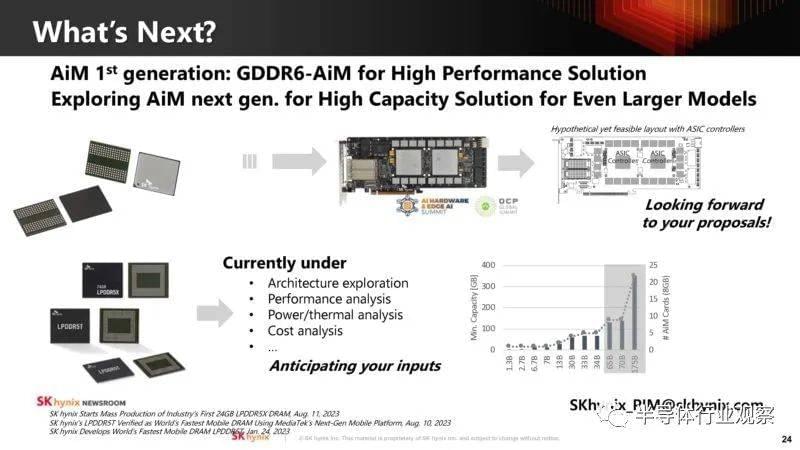

SK 海力士仍处于评估阶段,对该解决方案与更传统的解决方案进行不同类型的分析。

SK 海力士和三星多年来一直在谈论内存计算。看看未来是否有大客户采用这一点将会很有趣。目前看来,下一代人工智能计算本质上将更加传统,但这也许是几年后将会起飞的领域之一。

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:编辑部