让我们来还原以下这个新闻本身。

美国企业推出了0.7nm芯片?

这其实是来自美国Zyvex Labs的一个报道。

在9月21日, Zyvex Labs宣布,推出世界上最高分辨率的光刻系统 — ZyvexLitho1。该工具使用量子物理技术来实现原子精度图案化和亚纳米(768 皮米——Si (100) 2×1 二聚体行的宽度)分辨率。

这一进步使量子计算机能够为真正安全的通信提供牢不可破的加密;还更快的药物发现和更准确的天气预报。

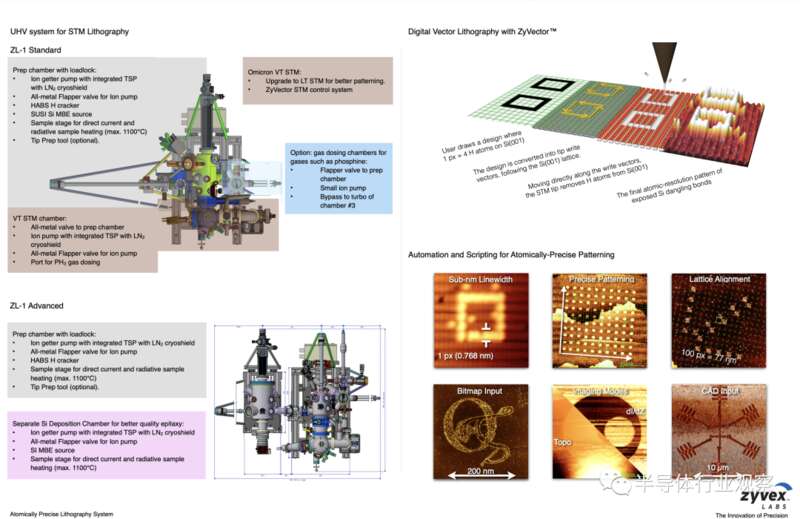

报道进一步指出,ZyvexLitho1 是一款基于扫描隧道显微镜 (STM:Scanning Tunneling Microscopy) 仪器,Zyvex Labs 自 2007 年以来一直在改进该仪器。ZyvexLitho1 包含许多商业扫描隧道显微镜所不具备的自动化特性和功能。

“构建可扩展的量子计算机存在许多挑战。我们坚信,要实现量子计算的全部潜力,需要高精度制造,”Michelle Simmons 教授说。“我们对 ZyvexLitho1 感到兴奋,这是第一个提供原子精度图案化的商用工具。”

STM 光刻技术的发明者 Joe Lyding 教授表示:“迄今为止,Zyvex Labs 技术是这种原子级精确光刻技术的最先进和唯一的商业化实现。” Lyding 是 2014 年费曼奖获得者,也是伊利诺伊大学电气与计算机工程专业的 Robert C. MacClinchie 特聘教授。

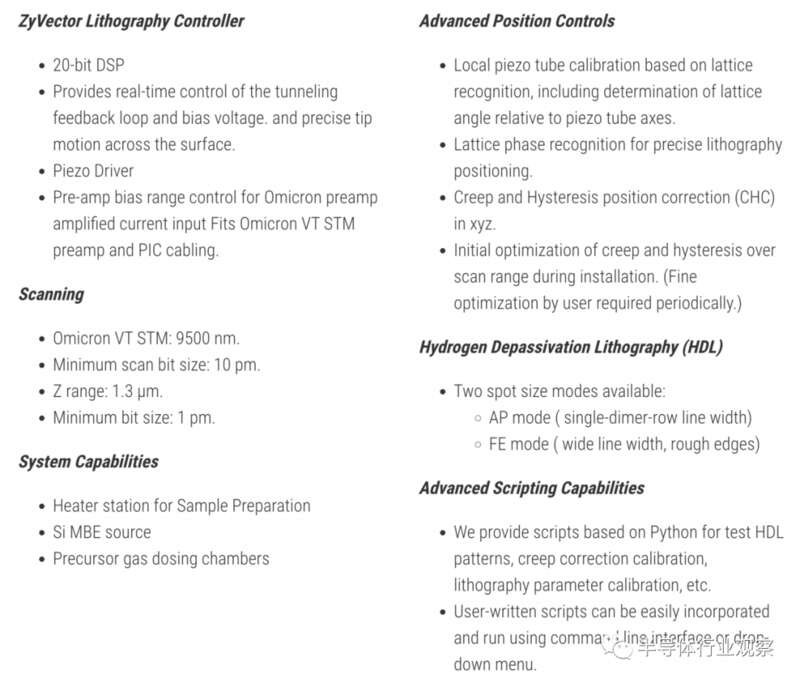

ZyvexLitho1 中嵌入的是我们的 ZyVector。这种具有低噪声和低延迟的 20 位数字控制系统使我们的用户能够为固态量子器件和其他纳米器件和材料制作原子级精确的图案。完整的 ZyvexLitho1 系统还包括配置用于制造量子器件的 ScientaOmicron 超高真空 STM。

“我期待继续与 Zyvex 进行富有成效的合作,”ScientaOmicron 产品经理 SPM Andreas Bettac 博士评论道。“在这里,我们将最新的 UHV 系统设计和 ScientaOmicron 久经考验且成熟的 SPM 与 Zyvex 用于基于 STM 的光刻的专用高精度 STM 控制器相结合。”

从报道可以看到,该产品还得到了美国DARPA(国防高级研究计划署)、陆军研究办公室、能源部先进制造办公室和德克萨斯大学达拉斯分校的 Reza Moheimani 教授的支持,后者最近获得了工业成就奖国际自动控制联合会授予“支持在单原子尺度上制造量子硅器件的控制发展”奖。

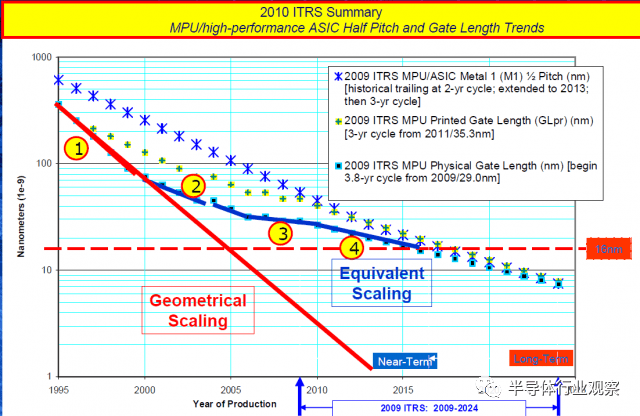

对半导体行业有了解的读者应该清楚,我们平时所谓的多少纳米,其实是一个工艺节点的代号。通常意义上,这个代号是用一个数字命名,后跟纳米的缩写,例如7nm、5nm、3nm 等。

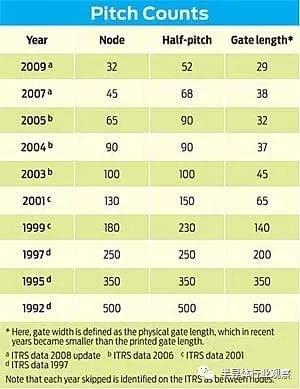

从大约 1960 年代到 1990 年代末,节点是根据它们的门长度命名的。这张来自 IEEE 的图表显示了这种关系。

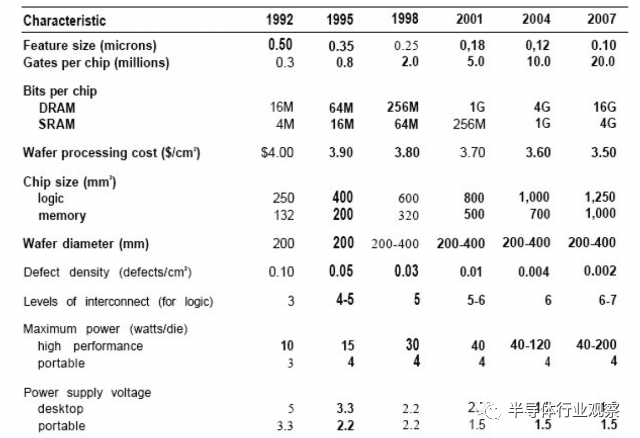

半导体制造涉及巨大的资本支出和大量的长期研究。从论文中引入新技术方法到大规模商业制造之间的平均时间长度约为 10-15 年。

几十年前,半导体行业认识到,如果存在用于节点引入的通用路线图以及这些节点将针对的特征大小,这将对每个人都有好处。

这将允许广泛、同时开发将新节点推向市场所需的所有难题。多年来,ITRS(国际半导体技术路线图)发布了该行业的总体路线图(已经停止更新了)。这些路线图跨越 15 年,为半导体市场设定了总体目标。

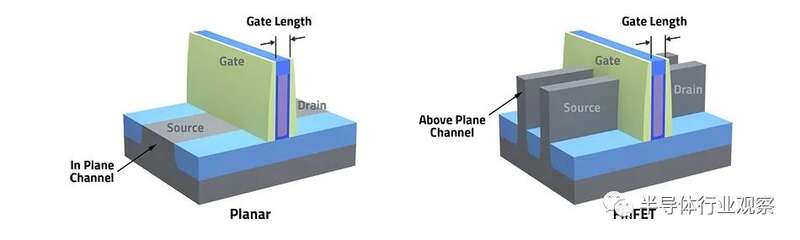

长期以来,栅极长度(晶体管栅极的长度)和半间距(芯片上两个相同特征之间距离的一半)与工艺节点名称相匹配,但上一次出现这种情况是在1997 年。pitch 继续匹配节点名称几代,但在任何实际意义上不再与它相关。

由此可见,这在工艺上与我们熟悉的工艺节点是不太一样。至于这个光刻,则是所谓的STM光刻。

绕开EUV光刻技术?

从相关报道指出,达成这个0.7纳米分辨率的光刻系统这是一种称为氢去钝化光刻(Hydrogen Depassivation Lithography )的技术,它是一种电子束光刻技术 (EBL),可实现原子分辨率。

据维基百科介绍,电子束光刻(通常缩写EBL)是扫描聚焦电子束以在覆盖有称为光刻胶(曝光)的电子敏感膜的表面上绘制自定义形状的做法。

电子束改变了光刻胶的溶解度,通过将抗蚀剂浸入溶剂中(显影),可以选择性地去除曝光或未曝光区域。与光刻一样,其目的是在抗蚀剂中创建非常小的结构,然后通常通过蚀刻将其转移到基板材料上。

电子束光刻的主要优点是它可以绘制具有sub-10 nm 分辨率的自定义图案(直接写入) 。这种形式的无掩模光刻具有高分辨率和低产量,限制了其用于光掩模制造、半导体器件的小批量生产以及研发。

据介绍,该机器的用途包括为基于量子点的量子比特制作极其精确的结构,以实现最高的量子比特质量。该产品可用于其他非量子相关应用,例如构建用于生物医学和其他化学分离技术的纳米孔膜。

如上所述,该产品的缺点是吞吐量非常低,换而言之,它可能适合制造小批量的量子处理器芯片,对于大批量消费电子产品来说,这不是一个好的解决方案。

Zyvex Labs在官网中也表示,该系统能够使原子精密光刻成为现实,当中用于 STM 光刻的 UHV 系统 、前体气体计量和 Si MBE 、数字矢量光刻和自动化和脚本。

他们表示,如果没有亚纳米分辨率和精度,这种 7.7 纳米(10 像素)正方形的曝光是不可能的。

Zyvex Labs指出,ZyvexLitho1 使用氢去钝化光刻从 Si (100) 2×1 重建表面去除 H 原子。这种自我显影的曝光技术本质上是二元的。

H-Si 键要么断裂(将 H 原子送入真空),要么没有。没有部分暴露或邻近效应。利用这个过程和作为硅表面晶格的全局基准网格允许数字光刻。

亚纳米像素是 4 个表面硅原子。可以将设计网格与我们的像素网格相同的计算机辅助设计 (CAD) 文件加载到 ZyvexLitho1 中,并且可以自动将图案分割成不同的几何形状,从而允许尖端矢量与不同的光刻模式一起使用。然后可以自动进行曝光。

他们还强调,由于光刻模式和成像模式在能量上分离良好,因此可以在光刻前后对Si表面进行成像。这种非曝光成像模式允许自动识别硅晶格,因此可以自动识别像素在表面上的位置。这种 Lattice Lock 过程自动保持尖端定位(以及因此光刻)准确。

从他们提供的表格上看,该系统拥有以下特点:

那么,关于这个的讨论又来到了——EBL能取代传统光刻吗?

EBL能成为新选择吗?

所谓光刻,是芯片制造中的一种图案化工艺。该过程涉及将图案从光掩模转移到基板。这主要是使用配备有光学光源的步进器和扫描仪来完成的,这也是我们现在主流的芯片制造方式,大家熟悉的EUV和DUV就是使用这种方式的。

其他形式的光刻包括直写电子束(direct-write e-beam)和纳米压印( nanoimprint)。在研发中还有几种下一代光刻(NGL)技术——如多光束电子束和定向自组装(DSA)。

据美国NIST方面介绍,电子束光刻允许精细控制纳米结构特征,这些特征构成多种器件技术的基础。让10 nm 的横向分辨率、1 nm 的放置精度和 1 mm 的图案化区域都是可能的。

然而,实现这些性能指标取决于许多特定于样品的相互依赖的因素——图案定义和断裂、基板和掩模材料、曝光前和曝光后工艺、对准特征定义——以及关键的细节光刻系统的操作。

NIST表示,作为一项核心能力,其开发的工艺处于或接近传统电子束光刻技术的极限,以推进各个领域的纳米级设备和测量科学,例如:

用于精确计时的芯片级频率梳;用于波长和量子频率转换的非线性集成光学;用于传感、转换和非线性动力学研究的片上腔光机械和微/纳米机电系统;具有用于量子信息的非线性和量子发射器光源的量子光子集成电路;从紫外到红外的超表面,用于捕获和探测原子和离子、偏振测量、成像和时空超快激光脉冲整形;用于像差校正的光学显微镜标准。

但正如很多报道中所说,其吞吐和准确度,限制了EBL的发展。根据eBeam Initiative的一份调查显示,使用类似电子书光刻这样的直写设备制作一份掩膜写入时间大概在2.5到13个小时不等,其平均数在6.8个小时。

根据该组织的报告,对于复杂掩膜而言,最长写入时间在14到60个小时。一般来说,制造商们对于写入时间超过24个小时的掩膜设计方案会比较头疼。因为过长的写入时间就意味着更高的成本,更长的处理时间和良率问题。

得出的结论是,传统技术前进虽然很难,包括ASML的CTO在文章《EUV光刻机何去何从》中也承认了这一点。

但毫无疑问,这依然是芯片制造技术的主流。