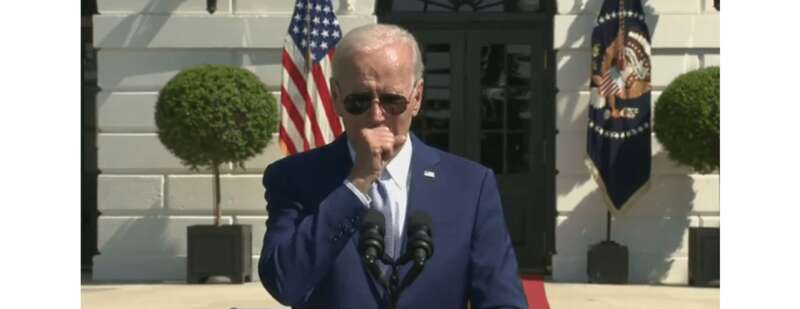

但是对于新冠初愈的美国总统拜登而言,这天显得格外辛苦:伴随着持续不断地咳嗽,他在一众半导体行业CEO的注视下,签署了延期许久的《2022芯片与科技法案》。

与传统的产业法案相比,《芯片与科学法案》给出了不少建议。其中有一条,显得格外的醒目:

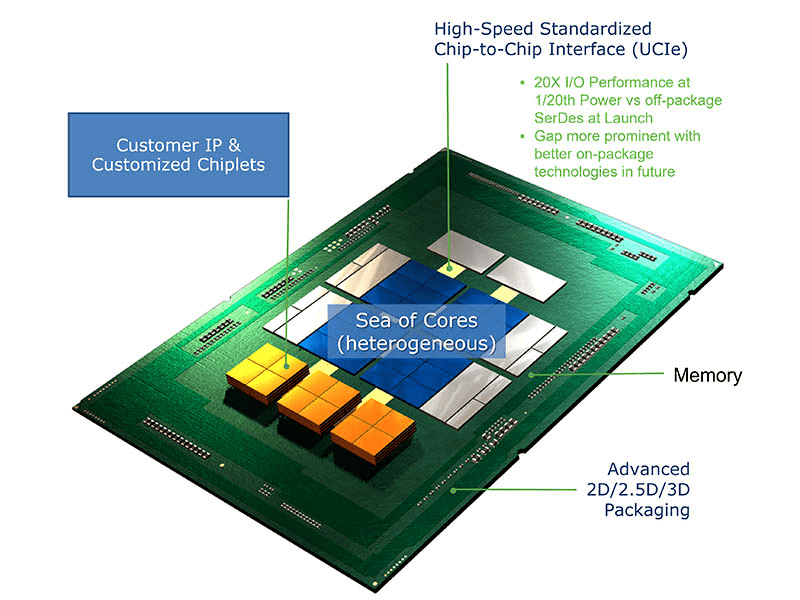

“我们还将建议开发‘芯粒平台(Chiplet Platform)’——一种包括产品中常见的、非创新部分的芯片——使初创公司和学术研究人员能够更快地创新,并大幅降低他们的开发成本。”

“我们还将建议开发‘芯粒平台(Chiplet Platform)’——一种包括产品中常见的、非创新部分的芯片——使初创公司和学术研究人员能够更快地创新,并大幅降低他们的开发成本。”

为了强调这一建议的价值,法案“恰到好处”地搬出了中国:

“其他国家,尤其是亚洲国家,正在进行投资,以降低进入市场的成本,并看到了成效。例如,中国每年创建的半导体初创公司是美国的六倍。”

“撰写这套法案的人是生搬硬套。”半导体从业人员林腾(化名)表示,“Chiplet不是平台,而是一种生产模式,是整个行业的改良。”

化整为零、灵活生产

Chiplet是什么?把“大芯片”拆成“小芯片”。

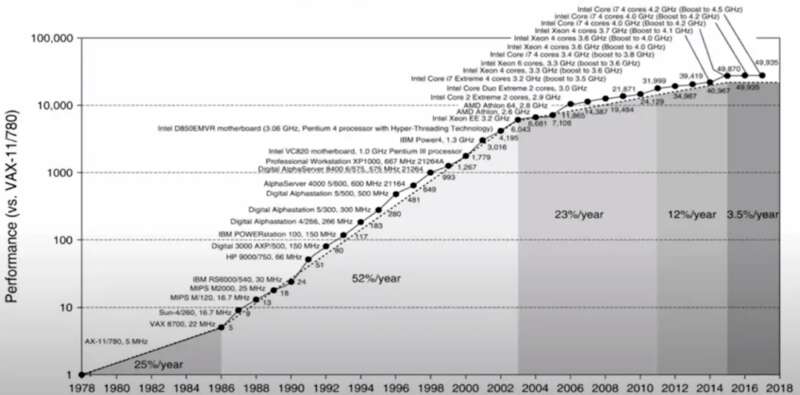

芯片行业的发展,理论上遵循摩尔定律:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

这一定律也奠定了芯片行业的大趋势:空间有限,数量翻倍。就要缩小晶体管体积,用先进制程提升性能。制程越先进,需要集成的晶体管越多,出现生产缺陷的可能性越大,芯片成本越高。

28nm制程前,摩尔定律顺风顺水。但是到了16nm/14nm时代,芯片设计成本攀升到了上亿美元,建厂成本达到150亿美元。受益于摩尔定律的CPU、DRAM等产品,性能提升却缓慢,并没有从先进制程中获益。

压缩晶体管,已经让芯片内卷到了极限。想进一步提高芯片集成度,就要从结构下手。

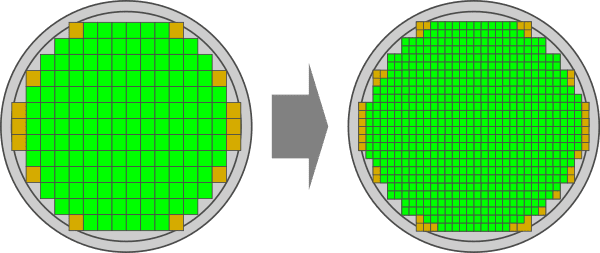

目前而言,芯片行业主流制造模式是系统级芯片(SoC),把不同功能模块封装在一个芯片中,各个模块都采取相同的制程。芯片面积越大,晶体管越多,SoC模式面临的压力就越大。

Chiplet模式则反其道而行之,把模块进行分类,先封装几个裸片,最后统一封装。构成芯片的几个模块,像积木一样分类组装,难度下降了不少。

既然是分块组装,各个模块就能自行配置,降本增效。利用Chiplet组装的芯片,CPU可能是10nm,存储芯片可能是14nm,模拟芯片可能是90nm。

林腾算了一笔账:“28nm SoC 芯片成本为5000万美元,7nm为3亿美元。如果用Chiplet模式平衡成本,可以省出20%的资金。”

利用化整为零的策略,Chiplet还提高了芯片良品率。芯片良品率与芯片面积有关,同样大小的晶圆,芯片加工面积越大,芯片生产数量越少,因为生产缺陷淘汰的芯片比例越高。Chiplet按模块生产,提高了芯片加工数量,从而提高了良率。

除此之外,Chiplet模式下生产的模块,可以根据需要迁移到其他的芯片设计中。将设计资源进行整合,不但降低了芯片的设计成本,也可以让企业根据市场需求迭代产品,加速产品上市。

中国企业、积极追赶

模块生产,灵活配置的Chiplet模式,也为中国芯片产业提供了新机会。

国内大厂的Chiplet项目中,最为知名的是华为鲲鹏920芯片,该芯片与2019年量产,将7nm逻辑芯片与16nm I/O芯片等集成在SoC中,主要用于华为TaiShan服务器。中国移动今年2月公布的2021-2022第1批PC服务器集采项目中,基于华为鲲鹏芯片的服务器占比达到16.55%,拥有着出色的市场反馈。

但是华为在Chiplet领域的投入,要追溯到2014年。当时华为海思半导体与台积电合作生产了一款64位Arm架构服务器处理器。使用了台积电开发的CoWoS封装技术,集成16nm逻辑芯片与28nm I/O芯片。用Chiplet加强服务器业务实力,将是华为的长期战略。

在Chiplet模式涉及的封装流程中,国内企业也在加紧发力。国内第一大封测企业长电科技,就在去年推出了XDFOI技术。该技术是一种面向Chiplet的极高密度,多扇出型封装高密度异构集成解决方案,可以覆盖2D/2.5D/3D Chiplet,适应多种异构封装产品。

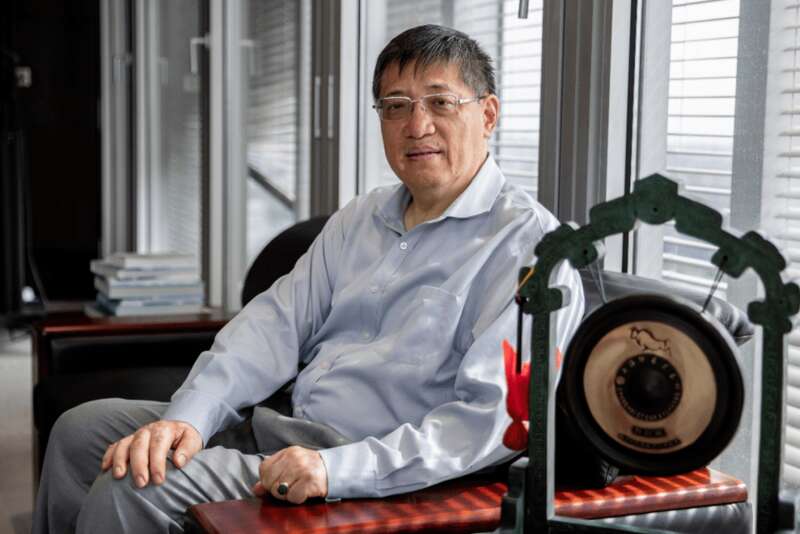

追溯到行业源头,芯片IP供应商也在参与Chiplet。作为国内知名芯片IP企业,芯原股份在2020年就公开表示布局Chiplet业务,公司通过Chiplet架构设计推出了高端应用处理器平台,从定义到流片仅用了12个月,工程样片回片当天顺利点亮,并在样机中顺利运行。公司推出的12nm Chiplet产品正在自动驾驶域控制器上开展验证工作,正在进行版本迭代。

与华为,AMD,英特尔等厂商将Chiplet资源投入到服务器领域相比,执掌芯原股份的戴伟民十分看重Chiplet在自动驾驶领域的发展,他也给出了自己的分析:

“把计算和功能模块以Chiplet的方式单独做好车规验证工作,然后通过增加这些Chiplet来升级汽车芯片,可以大幅简化汽车芯片迭代时的设计工作和车规流程,同时增加汽车芯片的可靠性——因为几颗Chiplet同时失效的几率远远小于一颗汽车芯片失效的几率。”

机遇初现、挑战仍在

Chiplet给芯片行业带来的,不光是蓝图,还有挑战。

首先,Chiplet实现“模块化生产”的前提,是各个配件拥有统一的连接协议,从而灵活适应系统拓展需求和性能指标。但是目前Chiplet标准建立还处于早期阶段,缺乏统一标准。

3月2日,半导体巨头AMD、ARM、Google云、Intel、Meta、微软、高通、三星、台积电宣布成立行业联盟,打造Chiplet互联标准“UCIe”(Universal Chiplet Interconnect Express)。今年年底,由工信部电子四院,中科院计算所等机构制订的《小芯片接口总线技术要求》即将公布。建立独立生态,对接全球市场,对于国内芯片企业是全新的挑战。

另一方面,Chiplet模式的成立需要充足的芯片IP资源。不同厂商生产的Chiplet产品,也需要跨平台的EDA软件进行同步。国内芯片企业目前对国外EDA和IP供应商依赖度较高,要创造开放的Chiplet开发环境,依然需要国内相关企业的支持。

除此之外,Chiplet在生产模式上的优化,离不开先进封装技术的深度应用,在跨厂商、跨制程的生产环境下设计布局。与英特尔、台积电等厂商相比,国内封测厂商缺乏有行业说服力的技术路线,国内代工厂需要持续进行技术整合,形成行业共识。

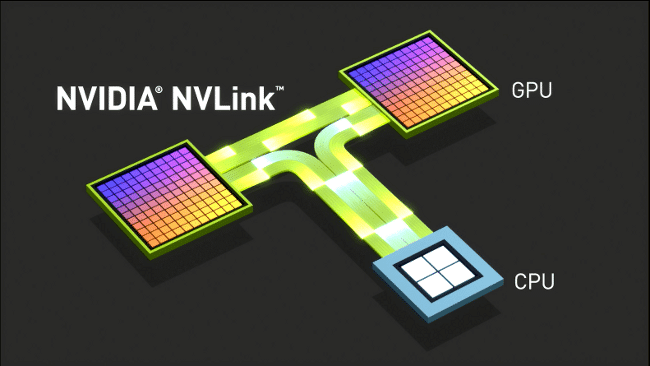

如果技术路线不同,Chiplet也很难大展拳脚。英伟达副总裁伊恩·巴克就表示,虽然英伟达曾经遇到光掩膜问题,无法打印大面积芯片,但是公司并没有选择Chiplet方案。因为英伟达采用的GPU运算,是利用上千个计算内核依次执行大量相对简单的计算。

为了规避这个问题,英伟达开发了NVlink技术,通过连接两块 NVIDIA 显卡,能够实现显存和性能扩展。这项点对点连接技术也用于英伟达GPU和CPU之间的高速连接,让GPU动用CPU的资源。英伟达的“超级芯片”计划,也不采用Chiplet的生产模式。

“摩尔定律和Chiplet的讨论,本质是围着DRAM和CPU转。”林腾表示,“这些讨论成立的前提,是高性能产品发展乏力,需要生产层面的优化。Chiplet发展比较成功的AMD,目标也是数据中心。如果在国内,还是服务器和汽车领域应用更有潜力,继续推广难度也不小。”