本文来自微信公众号:半导体行业观察 (ID:icbank),作者:编辑部,头图来自:视觉中国

知名分析机构集邦咨询昨天表示,英特尔计划将 Meteor Lake 的tGPU芯片组外包给台积电制造。按照计划,他们的最初量产计划在 2H22 进行,但后来由于产品设计和工艺验证问题推迟到 1H23。近日,该产品的量产计划因故再次推迟至2023年底,几乎完全取消了原定于2023年预定的3nm产能,仅剩下少量晶圆投入用于工程验证。

按照集邦的说法,此次事件对台积电的扩产计划造成了影响很大,导致苹果成为2H22至2023年初第一波3nm制程客户中唯一一家,产品包括M系列芯片和A17 Bionic。有鉴于此,台积电决定放慢扩产进度,以确保产能不会过度闲置,导致巨大的成本摊销压力。除了正式通知设备供应商公司有意调整2023年设备订单外,由于3nm扩产成本高昂,集邦咨询预计此举还将影响台积电2023年CapEx计划的部分内容。因此,台积电 2023 年的资本支出规模可能低于 2022 年。

值得一提的是,虽然英特尔大幅调整2023年外包计划,导致台积电推迟2023年扩产计划,但放眼AMD、联发科、高通等其他先进制程客户,这些公司都陆续计划到2024年量产其3nm产品2024 年。同时,苹果 2024 年新款 iPhone 有望全面采用 3nm 处理器。上述客户的引入,将为台积电2024年的3nm产能利用率和营收表现注入动力。

根据台积电技术论坛资料,位于南科Fab 18厂区的P5~P9厂等共5座12吋厂兴建计划已启动,他们将成为公司3纳米的主要生产重镇,而这次传言变动,将会给台积电带来新的不确定性。

对于记者提问相关消息,台积电回应指出:“台积公司不评论个别客户业务。公司产能扩充项目按照计划进行。”另外,调研机构以赛亚调研也指出,3/5nm等先进制程有八成左右是共用机台,因此台积电可以根据其他制程客户的需求弹性调配。

一、未来三年,五种3nm工艺

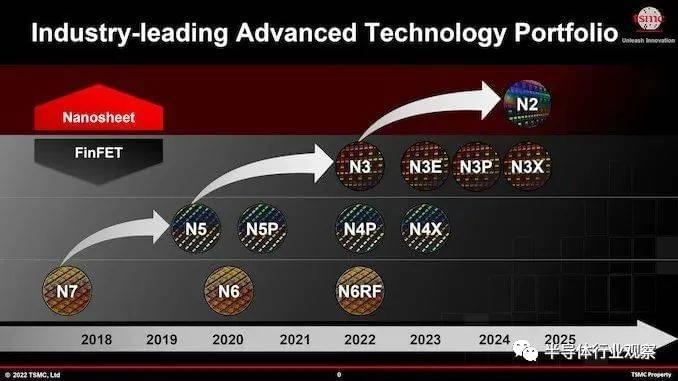

在早前举办的技术研讨会上,台积电宣布的关键事项之一是其属于其 N3(3 纳米级)这些先进节点,它们将在未来几年用于制造先进的 CPU、GPU 和 SoC .N3:未来三年的五个节点

随着制造工艺变得越来越复杂,它们的寻路、研究和开发时间也变得越来越长,因此我们不再看到台积电和其他代工厂每两年就会出现一个全新的节点。在 N3 中,台积电的新节点引入节奏将扩大到 2.5 年左右,而在 N2 中,它将延长到 3 年左右。

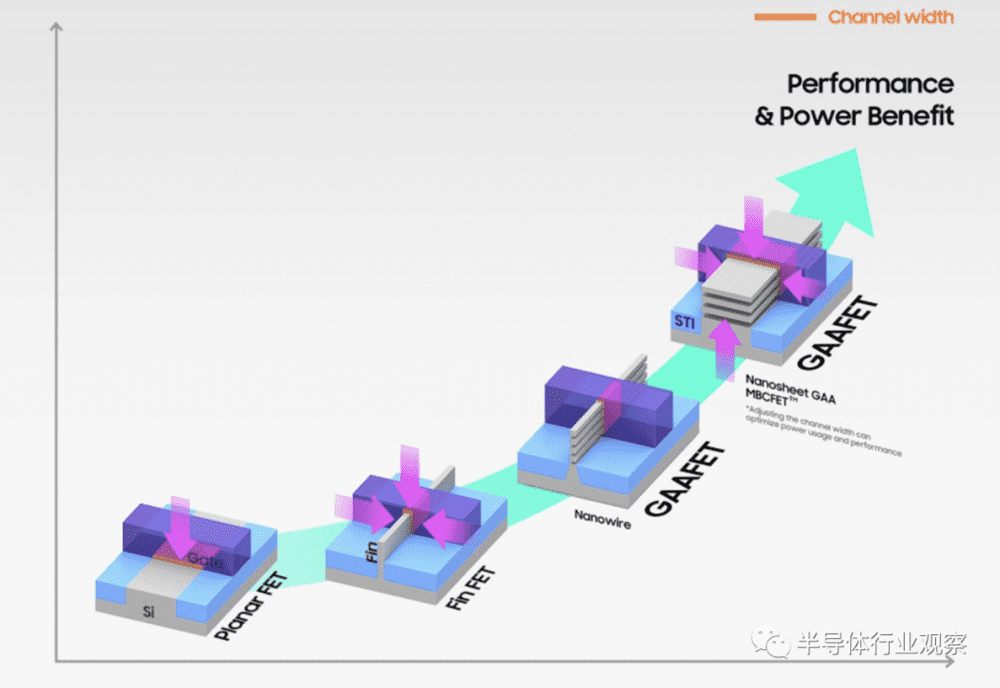

这意味着台积电将需要提供 N3 的增强版本,以满足其客户的需求,这些客户仍在寻求每瓦性能的改进以及晶体管密度每年左右的提升。台积电及其客户需要多个版本的 N3 的另一个原因是,代工厂的 N2 依赖于使用纳米片实现的全新栅极环绕场效应晶体管(GAA FET),预计这将带来更高的成本、新的设计方法、新 IP 和许多其他变化。虽然尖端芯片的开发人员将很快转向 N2,但台积电的许多普通客户将在未来几年坚持使用各种 N3 技术。

在其 2022 年台积电技术研讨会上,该代工厂谈到了将在未来几年推出的四种 N3 衍生制造工艺(总共五个 3 纳米级节点)——N3E、N3P、N3S 和 N3X。这些 N3 变体旨在为超高性能应用提供改进的工艺窗口、更高的性能、增加的晶体管密度和增强的电压。所有这些技术都将支持 FinFlex,这是 TSMC 的“秘密武器”功能,极大地增强了他们的设计灵活性,并允许芯片设计人员精确优化性能、功耗和成本。

1. N3 和 N3E:HVM 步入正轨

台积电的第一个 3 纳米级节点称为 N3,该节点有望在今年下半年开始大批量制造(HVM)。实际芯片将于 2023 年初交付给客户。该技术主要针对早期采用者(如Apple 等),他们可以投资于领先的设计,并从前沿节点提供的性能、功率和面积(PPA)中受益。但由于它是为特定类型的应用量身定制的,因此 N3 的工艺窗口相对较窄(产生确定结果的一系列参数),就良率而言,它可能并不适合所有应用。

这就是 N3E 发挥作用的时候。

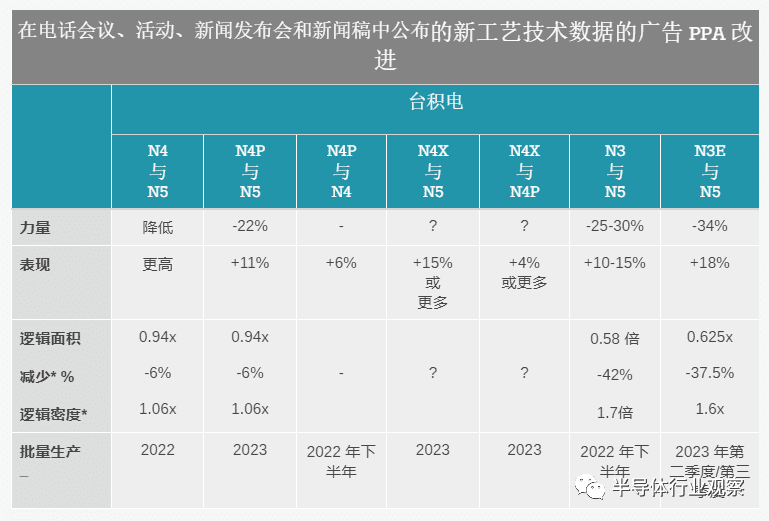

新技术提高了性能,降低了功耗,增加了工艺窗口,从而提高了良率。但权衡是该节点的逻辑密度略有降低。与 N5 相比,N3E 将提供 34% 的功耗降低(在相同的速度和复杂性下)或 18% 的性能提升(在相同的功率和复杂性下),并将逻辑晶体管密度提高 1.6 倍。

值得注意的是,根据台积电的数据,N3E 将提供比 N4X更高的时钟速度(2023 年到期)。不过后者也将支持超高驱动电流和1.2V以上的电压,在这一点上它将能够提供无与伦比的性能,但功耗非常高。

总的来说,N3E 看起来是比 N3 更通用的节点,这就是为什么台积电在这一点上拥有更多的“3nm 流片”,而不是在其类似的开发阶段拥有 5nm 级节点也就不足为奇了。

使用 N3E 的芯片的风险生产将在未来几周(即 2022 年第二季度或第三季度)开始,HVM 将在 2023 年中期开始(同样,台积电没有透露是在第二季度还是第三季度)。因此,预计商业 N3E 芯片将在 2023 年底或 2024 年初上市。

2. N3P、N3S 和 N3X:性能、密度、电压

N3 的改进并不止于 N3E。台积电将在 2024 年左右的某个时间推出 N3P,这是其制造工艺的性能增强版本,以及 N3S,该节点的密度增强版本。不幸的是,台积电目前没有透露这些变体将提供哪些改进到基线 N3。事实上,此时台积电在其路线图的所有版本中甚至都没有展示 N3S,因此尝试猜测其特性确实不是一个好生意。

最后,对于那些无论功耗和成本都需要超高性能的客户,台积电将提供N3X,它本质上是N4X的意识形态接班人。同样,台积电没有透露有关该节点的详细信息,只是表示它将支持高驱动电流和电压。我们可能会推测 N4X 可以使用背面供电,但由于我们谈论的是基于 FinFET 的节点,而台积电只会在基于纳米片的 N2 中实现背面供电轨,我们不确定情况是否如此。尽管如此,在电压增加和性能增强方面,台积电可能有许多优势。

3. FinFlex:N3 的秘诀

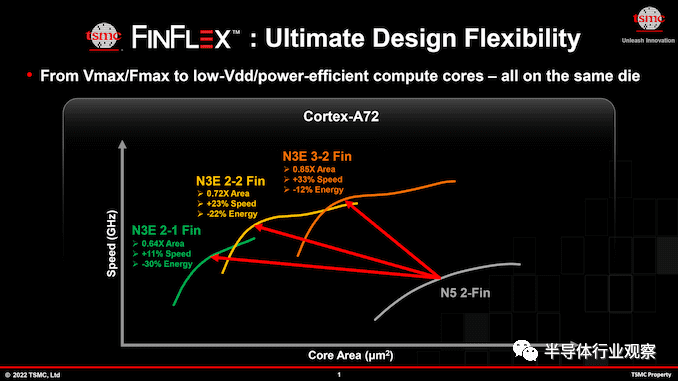

说到增强功能,我们绝对应该提到台积电 N3 的秘诀:FinFlex 技术。简而言之,FinFlex 允许芯片设计人员精确地定制他们的构建模块,以实现更高的性能、更高的密度和更低的功耗。

当使用基于 FinFET 的节点时,芯片设计人员可以在使用不同晶体管的不同库之间进行选择。当开发人员需要以性能为代价来最小化裸片尺寸并节省功耗时,他们会使用双栅极单鳍(2-1)FinFET(见图)。但是,当他们需要在芯片尺寸和更高功率的权衡下最大限度地提高性能时,他们会使用三栅极双鳍(3-2)晶体管。当开发人员需要平衡时,他们会选择双栅极双鳍(2-2)FinFET。

目前,芯片设计人员必须为整个芯片或 SoC 设计中的整个模块坚持一种库/晶体管类型。例如,可以使用 3-2 个 FinFET 来实现 CPU 内核以使其运行更快,或者使用 2-1 个 FinFET 来降低其功耗和占用空间。

这是一个公平的权衡,但它并不适用于所有情况,尤其是当我们谈论使用比现有技术更昂贵的 3 纳米级节点时。

对于 N3,台积电的 FinFlex 技术将允许芯片设计人员在一个模块内混合和匹配不同类型的 FinFET,以精确定制性能、功耗和面积。对于像 CPU 内核这样的复杂结构,这样的优化提供了很多提高内核性能的机会,同时仍然优化了裸片尺寸。因此,我们渴望看到 SoC 设计人员将如何在即将到来的 N3 时代利用 FinFlex。

FinFlex 不能替代节点专业化(性能、密度、电压),因为工艺技术比单一工艺技术中的库或晶体管结构有更大的差异,但 FinFlex 看起来是优化性能、功率和成本的好方法台积电的 N3 节点。最终,这项技术将使 FinFET 的灵活性更接近基于纳米片的 GAAFET 的灵活性,后者将提供可调节的通道宽度,以获得更高的性能或降低功耗。

与台积电的 N7 和 N5 一样,N3 将成为世界上最大的半导体对比度制造商的另一个持久节点系列。尤其是随着台积电在 2nm 阶段转向基于纳米片的 GAAFET,3nm 系列将成为该公司“经典”前沿 FinFET 节点的最后一个系列,许多客户将坚持使用几年(或者更多)。

反过来,这也是台积电为不同应用准备多个版本的 N3 以及 FinFlex 技术的原因,以便为芯片设计人员的设计提供一些额外的灵活性。

首批 N3 芯片将在未来几个月内投入生产,并于 2023 年初上市。同时,台积电在 2025 年推出 N2 工艺技术后,仍将继续使用其 N3 节点生产半导体。

二、三星:二代3nm也要来了

在台积电3nm生产计划有变的时候,三星则高歌猛进。在今年六月,三星表示,公司已经开始生产 3nm 芯片,在更节能的制造工艺上击败了竞争对手芯片制造商台积电。

三星表示,与之前的 5nm 工艺相比,新制造工艺的能效提高了 45%,性能提高了 23%,表面积缩小了 16%。未来,它希望其第二代3nm工艺能够分别降低50%和35%的功耗和35%的尺寸,并将性能提高30%。

该公告是三星努力与台积电竞争的一个重要里程碑,台积电主导着合同芯片生产市场,并且是苹果 iPhone、iPad、MacBook 和 Mac 芯片的制造商。不过据彭博社报道称,除非三星能够证明其新 3nm 工艺的成本效益与市场领导者具有竞争力,否则三星不太可能抢占台积电的市场份额。

三星表示,这些芯片最初将用于“高性能、低功耗计算”应用,但它计划最终将它们用于移动设备。彭博社指出,这些芯片目前将在韩国生产,最初在其华城工厂生产,然后扩展到平泽。

虽然三星第一代芯片并没有被大家看好。但根据报道,三星的第二代GAA芯片已经开始投入日程了。据外媒appuals报道,三星第二代3nm工艺将在2024年进行大规模出货。在爆料者Sravan Kundojjala的推文中,他保证三星可能会以其第二代 3nm芯片吸引手机制造商的注意。

在工艺方面推进的同时,三星在制造方面也有了很大胆的目标。据报道,随着美国国会准备批准 520亿美元来补贴扩大的美国半导体制造和研究,三星公布了在德克萨斯州建造 11 家新芯片厂的潜在计划,这个扩产的投资为1910亿美元。

在向德克萨斯州提交的第 313 章申请中(这是将导致该州为这些项目发放税收减免的长期规划过程的第一步)三星表示,11 个新工厂中的第一个将在 2034 年之前投入运营。然而,这家韩国企业集团强调,公开文件并未承诺三星将建造新的芯片工厂,该公司保留更改计划的权利。

需要强调一下,三星这个是一个潜在计划,如果成行了,必然会在产能上给韩国巨头带来很大的推动。不过,这目前也只是一个假设。

三、写在最后

其实无论是对于台积电、三星甚至英特尔,先进工艺还是给他们带来了很多机会。不过,正如之前的报道一样,最近全球的芯片扩产,给这个产业带来了更多不确定性,尤其是最近涉及先进EUV光刻机等设备的交货延迟,会给晶圆厂的扩产带来了不可控。

更重要一点,对于先进工艺来说,有头部客户一起去投入,并一起推动技术成熟,以降低成本会是新工艺持续推进的最大保证。现在传言中的英特尔的不不确定性,也给台积电带来了不确定性。

但毫无疑问,这是大势所趋。

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:编辑部