本文来自微信公众号:中国工程院院刊 (ID:CAE-Engineering),作者:Robert Pollie,原文标题:《纳米级芯片有望拯救摩尔定律丨Engineering》,头图来自:IBM

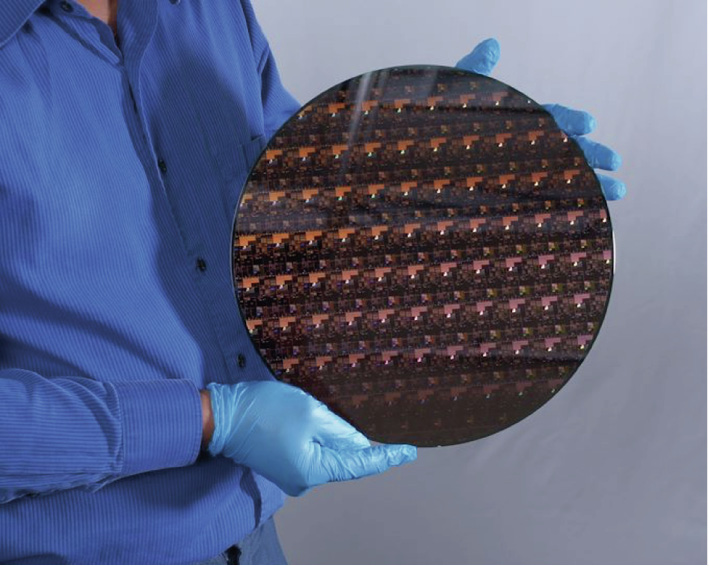

2021年5月,国际商业机器公司(IBM)的研发部门IBM研究院展示了其号称“世界第一款2 nm的芯片”(图1),至此半导体行业迎来了里程碑式的发展。测试芯片采用的是一种堆叠式纳米级芯片,提高了晶体管密度(每平方毫米的晶体管数),为研发更快、更节能的半导体铺平了道路。

美国马萨诸塞州剑桥市麻省理工学院电气工程学教授Jesús del Alamo说道:“纳米级芯片技术为摩尔定律提供了新的动力。我们认为,在未来几年里,芯片技术有望取得巨大进步。”

这是个好消息,因为在过去半个世纪里,摩尔定律一直是技术进步的推动力,推动着数字产品向更智能、更实惠、更高效的方向稳步发展。del Alamo指出,摩尔定律更光明的未来可能还会激励美国政府加大对旨在加强美国芯片生产力和竞争力项目的支持力度。他说道:“目前,美国正在讨论通过大规模投资,以在先进芯片技术方面重新获得领先地位。然而,只有当通过持续的技术改进能保持领先地位时,你才会进行大规模投资。”

摩尔定律认为每隔几年芯片密度就可以翻一番。近年来,一些观察人士预测,摩尔定律已不再适用。目前普遍采用的晶体管结构,即鳍式场效应晶体管(FinFET)遇到了重大的物理限制,无法进一步缩小。而纳米级芯片克服了这些障碍,使晶体管更进一步缩小并提高了晶体管的密度。具体来说,纳米级芯片采用“环栅”设计来严格控制电流并抑制FinFET的小规模漏电。

芯片晶体管作为微型电子开关,用金属栅极启动或关闭电流。在过去十年中,FinFET一直是普遍采用的晶体管结构。在FinFET中,载流通道由一个薄薄的、垂直的鳍片(由硅制成)组成,鳍片的三面与栅极相邻。问题在于,当晶体管尺寸变小时,FinFET栅极就无法完全关闭电流。即使晶体管处于“关闭”状态,电子仍会继续渗入通道,不但浪费电能,而且还会产生热量。

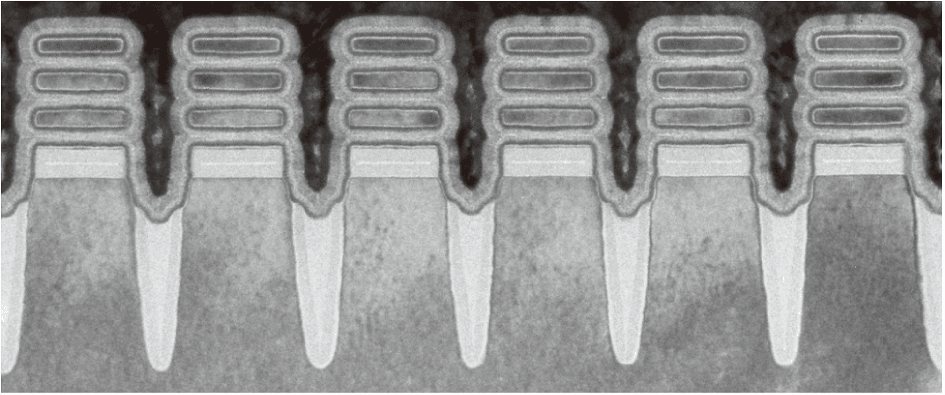

纳米级芯片晶体管用堆叠的水平硅片取代了FinFET的鳍形通道,每个硅片都被栅极材料完全包围(图2)。这种全方位的栅极覆盖(四面而不是三面)能更好地防止静电产生,并使晶体管在处于“关闭”状态时,最小化电子泄漏。

纳米级芯片还为设计提供了更大的灵活空间,让芯片制造商能够通过调整芯片的宽度来微调晶体管的性能和功耗(较宽的芯片通过的电流大,切换速度更快;较窄的芯片能限制电流和降低能耗)。相比之下,在FinFET中,鳍的尺寸是固定的,因此设计师只能通过改变鳍的数量进行粗粒度调整。

纳米级芯片的研发工作已历时多年。2017年,IBM研究院展示了这项技术的可行性,该公司称,工作中纳米级芯片晶体管可缩放至5 nm。IBM最新的纳米级芯片进一步巩固了这项技术。2 nm芯片上的晶体管密度比目前最前沿的7 nm芯片上的晶体管密度高出好几代,而且远远超过了FinFET要求的极限。对于FinFET来说,3 nm以下尺寸的芯片是不切实际的。请注意,“7 nm”“5 nm”“3 nm”并非对芯片特性的精确测量值,而是这个行业对半导体工艺发展等级(节点)的简称,每一个后续节点的晶体管密度大约是前一个节点的两倍。

IBM声称,其2 nm纳米级芯片技术可以让500亿个晶体管挤在一个150 mm2 (约为指甲盖大小)的芯片上;与最前沿的7 nm芯片相比,它的性能将提高45%,功耗将降低75%。

IBM研究院云计算中心的副总裁Mukesh Kahre说道:“我们预计2 nm技术将于2024年年底投产。” IBM不会自己生产芯片,该公司已在2014年停止生产半导体,而是准备与制造业伙伴合作,将这项技术商业化。美国加利福尼亚州圣何塞市半导体市场研究公司VLSI Research的首席执行官Dan Hutcheson说道:“在制造实用的2 nm测试芯片方面,IBM已经完成了最难的部分。现在我们面临的挑战是如何实现高产以及持续高产。”

Kahre表示,基于IBM纳米级芯片技术的芯片可能会被应用于各种类型的系统,从手持移动设备到高端服务器等。经过性能优化的2 nm芯片可以大大提高人工智能、自动驾驶汽车和机器学习等需要进行密集型处理的应用程序的处理效率,而低功耗版本则可以延长移动系统中电池的寿命,并减少数据中心的碳足迹。IBM很可能成为首批使用新型芯片的客户,并将其用于企业服务器的Power系列产品。

IBM并非唯一一家开展纳米级芯片研究的公司,三大半导体制造商都将这项技术列入了他们的发展蓝图。三星公司计划最快于2022年在3 nm芯片上使用其自主研发的纳米级芯片晶体管,即所谓的多桥通道场效应电子晶体管(MBCFET),而英特尔公司计划于2024年前推出其自主研发的“RibbonFET”纳米级芯片。据报道,中国台湾省积体电路制造股份有限公司(TSMC)将继续使用3 nm的FinFET,然后过渡到2 nm的纳米级芯片。

芯片制造商在纳米级芯片发展的浪潮中能走多远?Hutcheson认为,这项技术将会带来持久的影响,因为它为芯片设计开辟了一个新领域。他说道:“现在你可以将晶体管垂直放置了。你不仅可以将纳米级芯片堆叠在一起创建单个的晶体管,还可以将晶体管堆叠在一起。”这是因为,在纳米级芯片晶体管中,通道和其他元素是一层一层堆叠在硅基板上的。添加更多晶体管意味着堆叠更多层,就像在建筑物顶上再建一层。而在FinFET中,鳍形通道是从硅基板上切割出来的,因此晶体管被限制在“底层”,导致无法添加更多层。

英特尔公司已经演示了多晶体管叠加的过程,即使用纳米级芯片技术在P型金属氧化物半导体(PMOS)晶体管上搭载一个N型金属氧化物半导体(NMOS)晶体管。在传统设计中,这两种类型晶体管共同构成互补的金属氧化物半导体(CMOS)电路(芯片的基本组成部分),并排放置。通过将其堆叠放置,设计师可以将其原本占用的空间分成两半。这种向上堆叠而非向外扩展以节省空间的做法可能会为半导体技术带来深远影响。

Hutcheson说道:“即使不缩小晶体管,密度仍然可以增加。这是一项足以‘改变游戏规则’的技术。它提供了一种即使在核心技术遇到尺寸限制后也可以继续增加晶体管数量的方法。这是一种全新的提高逻辑半导体密度的方法。这就是我认为摩尔定律还可以继续适用10~20年的原因。”

人们对摩尔定律适用性的质疑可能已暂缓,但密度不可能永远持续增加。电路设计师只能在一个有限的空间内封装这些数量的晶体管。而研究人员却丝毫没有气馁。相反,他们正在探索其他方法来提高芯片性能和节省电力。例如,del Alamo及其在麻省理工学院的团队正在研究是否可以用砷化铟镓(InGaAs)等新材料替代传统上用于制造晶体管通道的硅。他说道:“这种化合物能让电子移动得更快,在其他条件相同的情况下,使用这种化合物可以获得更大的电流和更高的性能;或者相反,可以降低电压并降低功耗。但是,正如你想象的那样,使用这种化合物的同时也会出现许多新的挑战。”

改编原文:

Robert Pollie.Nanosheet Chips Poised to Rescue Moore’s Law[J].Engineering,2021,7(12):1655-1656.

本文来自微信公众号:中国工程院院刊 (ID:CAE-Engineering),作者:Robert Pollie