本文来自微信公众号:极客公园前沿社(ID:GeekParkFrontier),作者:捂耳朵 & flaash,原文标题:《一块不够再拼一块,苹果末代 M1 芯片让人瞥见微处理器的未来|HyperTech》,头图来自:视觉中国

12 年前,Apple 创始人 Steve Jobs 发布了第一台 iPad ,彼时他为这款平板电脑内的自制芯片(Apple A4)自信地承诺:“它会令人惊叹”。从那时起,Apple 便开始了其自研芯片的道路,现在这些芯片为 iPhone、Apple Watch 和 iMac 等一系列产品提供算力。

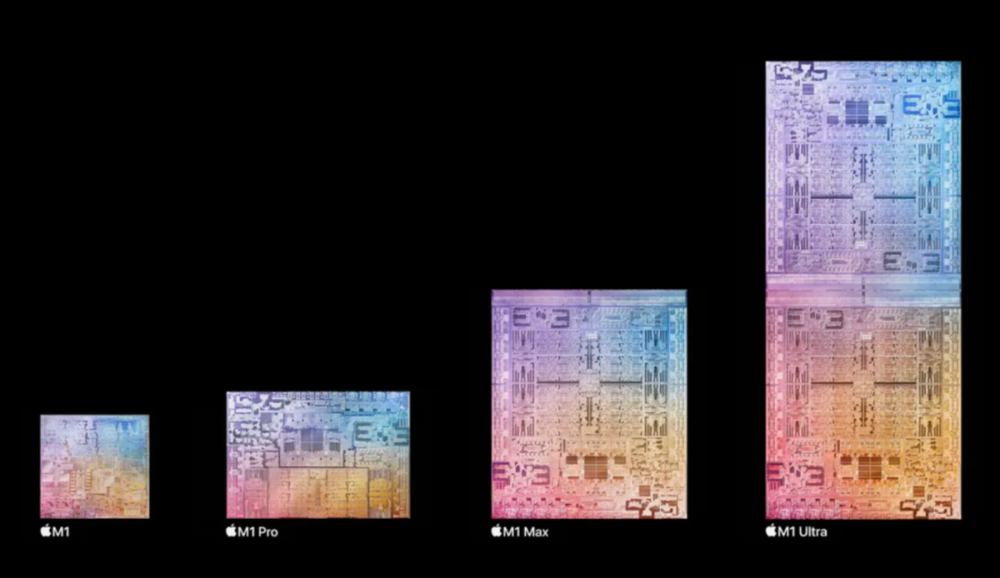

在推出 M1 Pro 和 M1 Max 芯片的仅几个月后,Apple 就在今年春季“Peek Performance”产品活动中揭开了 M1 系列 Apple Silicon SoC(System on Chip,片上系统) 最后一位成员的面纱。

上周二,Apple 发布了其最新的芯片——巨大的 M1 Ultra,它专门针对台式机设计,将会在 Apple 的新 Mac Studio 中首次亮相,成为 Mac Studio 的大脑。

“(M1 Ultra 是)Apple 芯片的 Game changer,它将再次震撼 PC 行业。”Apple 硬件技术高级副总裁 Johny Srouji 说。

一、后摩尔时代,苹果的“1+1 ”策略

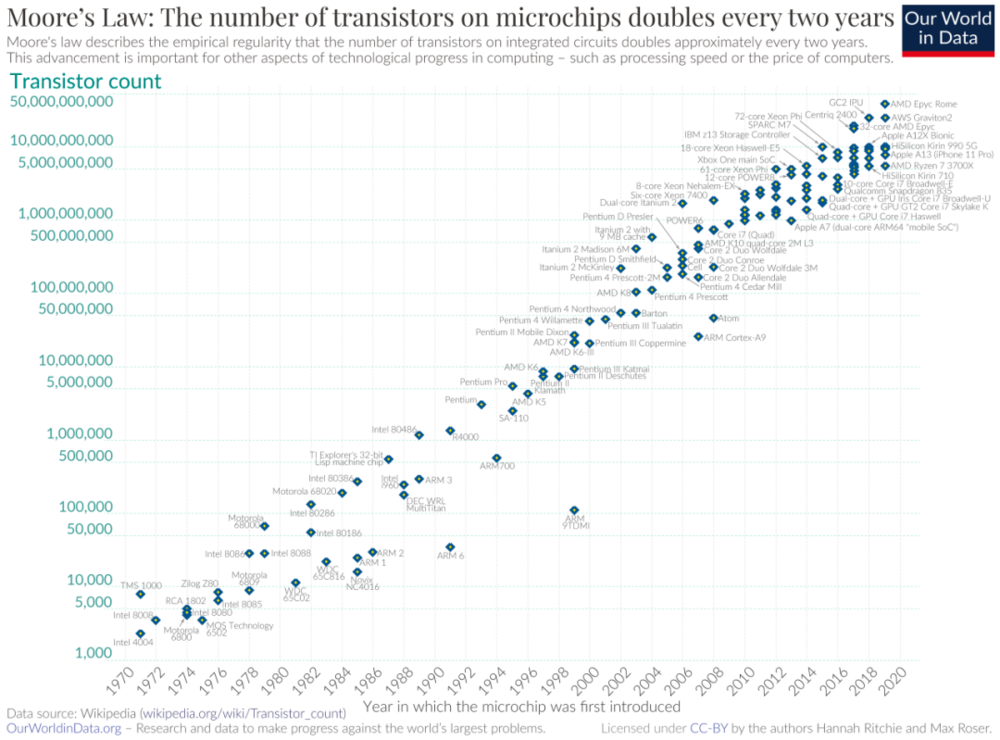

半导体行业大致按照摩尔定律(集成电路上可以容纳的晶体管数目在大约每 18 个月便会增加一倍)发展了半个多世纪。然而随着先进制程技术已经来到了 2nm 这一水平,晶体管大小正不断逼近原子的物理体积极限。与此同时,自动驾驶、5G、AI 等技术的发展仍在催促芯片性能的进一步提高。

可以说,在延续摩尔定律上,芯片制造商们遇到了挑战,而芯片组件的创造性封装(packaging)正在另辟蹊径地解决这一难题。Apple M1 Ultra 的“1+1”芯片设计思路或许揭示了微处理器的未来。

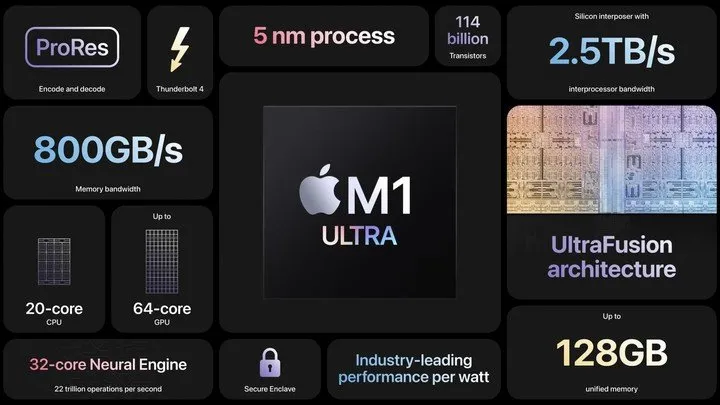

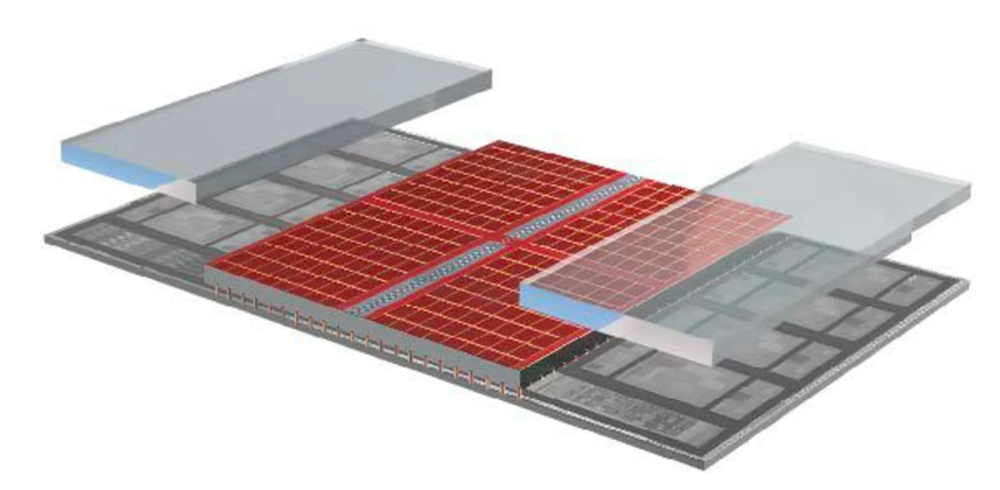

M1 Ultra 本质上是将两块 M1 Max 芯片“拼”在一起,它通过 Apple 所谓的 UltraFusion 封装架构结合了两个 M1 Max 芯片,提供每秒 2.5 TB 的低延迟、处理器间带宽。从概念上讲,它类似于 AMD 的 Infinity Fabric,能确保 CPU(中央处理器)、GPU(图形处理器) 和其他组件之间的快速通信。

采用台积电 5nm 工艺技术的 M1 Ultra 拥有 1140 亿个晶体管(这是个人电脑芯片中有史以来最多的),比原来的 M1 芯片增加了 7 倍。它的规格基本上等于将 2 个 M1 Max 芯片加在一起:它可以支持高达 128 GB 的统一内存,内存带宽为 800 GB/s。它包括 16 个具有 48MB L2 缓存的性能内核和 4 个具有 4MB L2 缓存的效率内核,而 GPU 最多可以有 64 个 GPU 内核。它还具有 32 核神经引擎,每秒可以执行高达 22 万亿次操作,以加速机器学习任务。

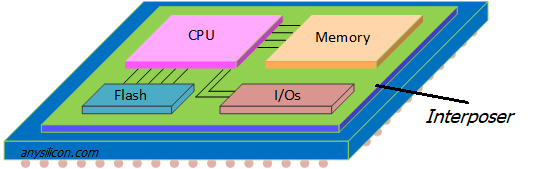

Digitimes 报道称,Apple 的 M1 Ultra SoC 使用台积电的 CoWoS-S(带有硅中介层的晶圆上芯片)基于2.5D 中介层的封装工艺。英伟达、AMD 和富士通使用类似的技术为数据中心和 HPC(高性能计算)构建高性能处理器。

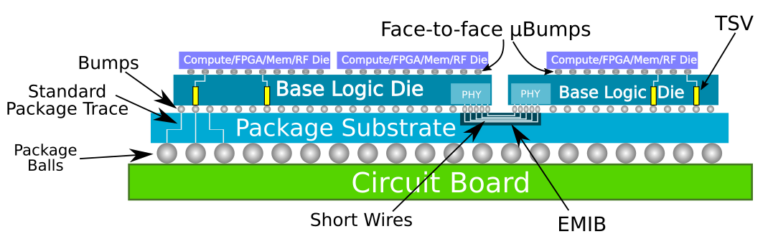

台积电在其用于超高带宽小芯片集成的 InFO_LSI(InFO 与 LSI 集成)技术中拥有 CoWoS-S 的更新的替代品。它使用局部硅互连而不是大型且昂贵的中介层,类似于英特尔的 EMIB(嵌入式芯片互连桥)。

据悉,Apple 选择 CoWoS-S 而不是 InFO_LSI,是因为后者没有及时为 M1 Ultra 做好准备。因此,Apple 很可能是选择了一种经过验证但更昂贵的解决方案,而不是更便宜、更新生的技术。

为了将处理器连接在一起,不仅仅 Apple 在开发创新封装技术。英特尔、AMD 和 Nvidia 也可以将多个裸片或小芯片组合成一个更大的处理器。M1 Ultra 可能是迄今为止最先进的概念实现,但它不会是最后一个。

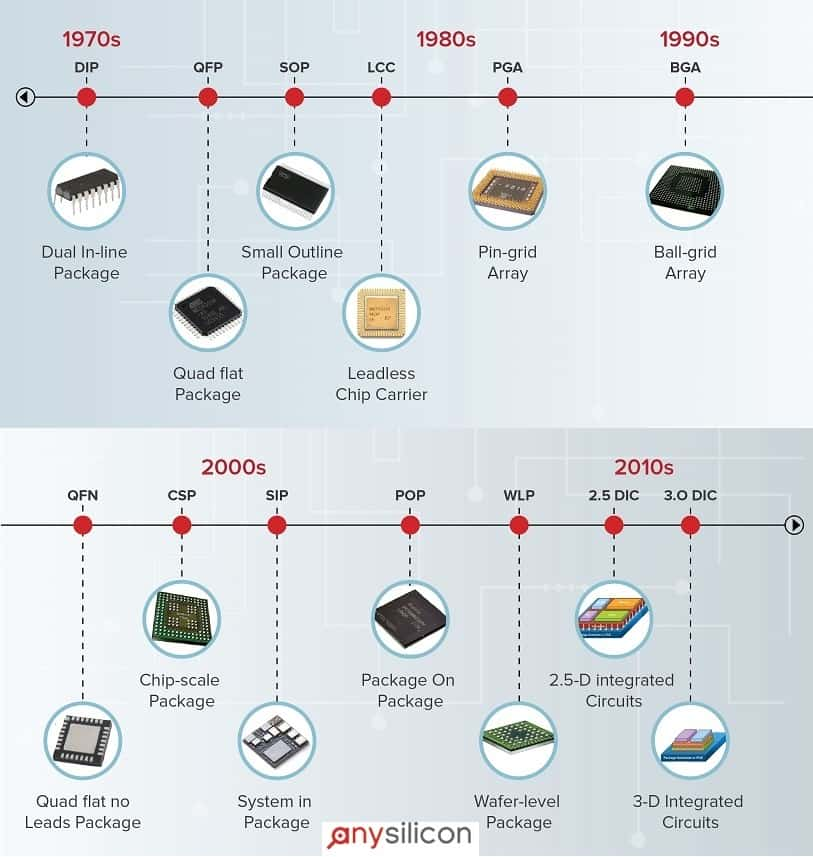

二、M1 Ultra 的 Ultra Packing

集成电路封装并不新鲜,但多年前它只是一种不大核心的技术,封装只是对芯片进行组装和保护。随着时间的推移,封装变得越来越复杂。近年来,保护性封装已经被尖端的通讯线路所取代,处理器制造商越来越认为更先进的封装技术是维持算力进步的重要部分。

Apple 的 UltraFusion 封装技术使用中介层(位于两个 M1 Max 芯片下方的薄硅片)用 10000 根电线将它们连接起来,每根电线能够在极短的距离内每秒传输 2.5 GB 的数据。为了确保一个芯片上的芯片内核可以访问另一个芯片上的内存,需要大量的处理能力。GPU 的内存消耗特别大。

从历史上看,中介层体积庞大且操作成本高。对于 M1 Max 芯片,Apple 使用了一种使用更薄切片的专有技术。

根据 Apple 的说法,UltraFusion 使用的硅中介层(silicon interposer)是其他竞争中介层技术的连接密度的两倍,带宽则是四倍。由于每个 M1 Max 的芯片面积为 432 mm²,因此 UltraFusion 中介层本身必须超过 864 mm²。这已经和 AMD 和 Nvidia 的企业级 GPU 采用 HBM(高带宽内存)的规模相同了。

英特尔创建的嵌入式多芯片互连桥(Embedded Multi-Die Interconnect Bridge)是一种类似的封装方法。一款名为 Sapphire Rapids 的高端服务器芯片预计将于今年晚些时候由英特尔发布,该公司尚未在市场上的任何芯片中使用 EMIB。Sapphire Rapids 将使用 EMIB 连接四个芯片和四个大内存模块。

Real World Technologies 的分析师 David Kanter 说,更昂贵和密集的 UltraFusion 线使苹果将数据从一个芯片传输到另一个芯片的速度几乎是英特尔使用 Sapphire Rapids 的 2 倍。

然而先进的封装并不能解决世界上所有的问题。M1 Ultra 是在体积和性能上是 M1 Max 的两倍,耗电量和产生的废热也是 M1 Max 的两倍。几乎可以确定,笔记本电脑一定无法很快配备它。

这样“拼”出的巨无霸芯片目前来看非常特别,但在未来会变得更加普遍。今年 3月 3 日,英特尔、台积电和三星宣布将携手建立先进芯片封装技术的行业标准,新联盟旨在建立一个名为 Universal Chiplet Interconnect Express(UCIe)的单芯片封装标准,以创建新的生态系统并促进封装和堆叠领域的合作。将不同类型的芯片(或所谓的小芯片)组合在一个封装中的更好方法可以创建更强大的芯片系统。

三、更先进的半导体封装即将到来

苹果的 M1 Ultra 只是创新封装的一个例子。在过去的几年里,更大的中介层已经变得流行起来,特别是对于 FPGA(Field-programmable gate array,现场可编程逻辑门阵列)——一个非常通用,但极度昂贵的处理器形式。最近几年,它也在被普遍接受的道路上取得了进展。

作为 Xeon 下一代处理器的一部分,英特尔发布了 Sapphire Rapids 芯片,其中包括一款将四个独立芯片组合到一个单独处理器中的芯片。芯片是使用 EMIB 进行连接,这是一种类似于中介层的 2.5D 封装方法,比以前利用的二维封装更上一层楼。

这项技术被称为 3D 封装,AMD CEO Lisa Su 正在使用它将芯片堆叠在一起。Ryzen 75800x3D 游戏 PC 处理器将在未来几周内首次使用这项技术。与传统数据传输相比,AMD 可以获得 15% 的性能提升,AMD 利用其 3D V-Cache 技术将高速存储芯片连接到 CPU 复合体中。

Foveros 是英特尔开发的一种 3D 堆叠技术,将用于 2023 年名为 Meteor Lake 的 PC 处理器上。

今年的 Ponte Vecchio 处理器、英特尔巨大的显卡和人工智能芯片都是为美国能源部的 Aurora 超级计算机设计的,它们结合了 EMIB 和 Foveros。“Ponte Vecchio 是先进包装的典范,”Kanter 说。

先进封装有一个主要缺点: 成本昂贵。Ponte Vecchio 就是一个很好的例子。芯片生产由于设计、采购、对齐和键合芯片的过程而变得更加困难和昂贵。

看看苹果就知道了,在 Mac Studio 上,花 1999 美元,你可以得到 M1 Max 版本,花 3999 美元你就可以得到 M1 Ultra 版本。要想使用 64 个 GPU 版本,还得额外支付 1000 美元购买最强大的版本的处理器。

Tech Insights 的 Gwennap 评论说,“是的,延续摩尔定律是可能的,我们可以继续把越来越多的晶体管封装进一个盒子里,但我们还没有做任何事来解决成本问题。”

原文链接:

1. Apple’s M1 Ultra Is a Glimpse Into the Future of Microprocessors

https://t.cn/A66MClnZ

2. Apple's M1 Ultra Chip Shows Healthy Future for High-Powered Macs

https://t.cn/A66MCTZt

本文来自微信公众号:极客公园前沿社(ID:GeekParkFrontier),作者:捂耳朵 & flaash