本文来自微信公众号:半导体行业观察 (ID:None),作者:龚佳佳,头图来自:视觉中国

时至今日,芯片设计巨头的高端系列芯片已经在7nm及以下的先进制程中搏斗。不仅如此,先进制程更是成为了台积电等代工龙头的“吸金密码”。

2021年台积电总营收为15874.2亿新台币(约合人民币3658.3亿元),其中,5纳米和7纳米合计营收占总营收50%,可以说扛起了台积电营收的半壁江山。

然而,随着高性能计算需求的增加,芯片制程的战火也逐渐从5nm蔓延到了3nm。3nm争夺战的“枪声”已经打响。

一、设计企业的“产能之争”

当前芯片已经来到了先进制程时代,鉴于能采用先进制程的代工厂只有台积电和三星两家,而需要先进制程工艺的芯片设计企业却有英特尔、苹果、高通、AMD、英伟达等数家,实打实处于“僧多肉少”的局面。对芯片企业来说,芯片工艺的比拼其实就是产品性能的比拼,为了不输给对手,芯片企业不得不开始上演一场“产能争夺战”。

从已经量产的5nm来看,业界传闻英伟达上个季度向台积电支付了 16.4 亿美元以保留其在 5nm中的份额,另外 17.9 亿美元将在 2022 年第一季度支付。据悉,英伟达将花费近 100 亿美元来确保其为 RTX 4080、4090 及其 40 系列提供 5nm 的芯片供应。

对于一个量产近2年,可以称得上是稳定良率的制程,英伟达都要斥百亿美元的巨资确保产能,可想而知,面对一个全新的制程,厂商的竞争只会更激烈,这决定着谁会是全球首款3纳米芯片。

目前来看,英特尔、苹果、高通、AMD等都已加入战局。

英特尔

虽然英特尔是IDM企业,但目前他在先进制程方面离3nm仍有距离。在2022年投资者大会上,英特尔曾表示Intel 4也就是7nm预计在2022年下半年投产;Intel 3(第二代7nm)预计在2023年下半年投产;Intel 20A(5nm)将于2024年投产;Intel 18A(第二代5nm)预计在2025年投产。

换句话说,英特尔的3nm还遥遥无期,但技术竞争并不会给英特尔喘息时间,此前由于英特尔无法按时生产7nm,导致AMD在CPU技术上领先,为了重返霸主宝座,英特尔必须争3nm。也正是因为这个原因,英特尔成为了台积电3nm 产能的竞争者之一,与苹果分庭抗礼。

去年有消息称,英特尔挤掉苹果成为台积电3nm工艺首批客户,主要生产其下一代处理器和图形产品。当时的供应链指出,英特尔下给台积电的产品包括一颗图形处理器及三个服务器处理器,首批数量约4000片,预计2022年5月正式产出交货,7月放量生产。

据业界报道,为了争抢产能,去年12月,英特尔CEO基尔辛格曾乘坐私人专机访台,希望争取到未来2~3年更多台积电先进工艺产能,涵盖制程包括7nm及优化后的6nm、5nm及优化后的4nm、以及3nm等。当时传言指出,对于3nm工艺,英特尔提出希望能与苹果一样,台积电能够为英特尔建造一条3nm产能特供专线。

一个月后,也就是2022年1月,就有消息传出台积电计划在其中国台湾北部的新生产基地专门开辟新产线为英特尔生产3纳米芯片,该生产基地位于新竹市宝山区。该消息人士称,英特尔希望台积电利用3nm制造工艺,为其生产CPU和GPU的零部件。

从上述来看,英特尔在争3nm产能中是打了一场漂亮的仗。

苹果

在此前发布的芯片线路图中,苹果预期在2023年发布基于3nm的第三代M系列芯片,并选择由台积电代工。

2020年时候,关于台积电3nm产能的新闻还都是“苹果是第一个和台积电签约3nm制程产能的厂商”、“全是苹果的,台积电3nm首批产能,iPhone全包”诸如此类,但计划永远赶不上变化,到了2021年下半年,英特尔的“横插一脚”让苹果失去了台积电3nm“独宠”的资格。

作为台积电十年老客户且还是最大的客户,苹果拥有的3nm产能应该不会少到哪里去,目前来看,为了台积电的3nm产能,苹果已经预付了大量的款项。但在4nm方面,苹果曾不得不接受台积电的涨价(但涨幅将低于其它先进制程客户)以确保产能,并包下12万片-15万片4nm产能(2022年平均价格约较2021年上涨8%-10%),到了3nm阶段,多少可能也会“历史再现”。

高通

去年12月曾有消息称高通有意导入三星 3nm 制程,但从最近的消息来看,情势可能生变。据韩媒报道,高通据称已将3nm AP处理器的订单交给台积电,将于明年推出,而造成订单转移的原因在于,三星的先进工艺节点面临产量问题。

高通也是台积电的重量级客户,此前有意将3nm订单交于三星也是因为争不过苹果在台积电的地位,为了确保足够的产能才转向三星,如今再传出将订单交给台积电说到底也是因为担心三星产量问题。

AMD

据台媒《工商时报》去年5月报道,AMD 已向台积电预订2022及后两年 5nm 及 3nm 产能,预计 2022 年推出 5nm Zen 4 架构处理器,2023年~2024 年间将推出 3nm Zen 5 架构处理器。不过和高通一样,AMD也曾传出了因为产能问题试图转单三星的消息,由此看出,3nm产能不够可能将成为台积电损失客户的“原罪”。

从当前的局势来看,随着本土GPU、DPU厂商的崛起,未来会有越来越多企业加入3nm的产能争夺战之中,届时局面相比当下或许会更加热闹。

二、代工厂的“3nm之战”

在芯片设计企业还在为产能“明争暗斗”的时候,晶圆制造领域又是另外一番景象。对晶圆制造厂来说,眼下更重要的是3nm的突破。谁率先量产了3nm,谁就将占领未来晶圆制造产业的制高点,甚至还会影响AMD、英伟达等芯片巨头的产品路线图。

毫无疑问,在3nm这个节点,目前能一决雌雄的只有台积电和三星,但英特尔显然也在往先进制程方面发力。不过从近日的消息来看,台积电和三星两家企业在量产3nm这件事上进行的都颇为坎坷。Gartner 分析师 Samuel Wang表示,3nm 的斜坡将比之前的节点花费更长的时间。

台积电

近日,一份引用半导体行业消息来源的报告表明,据报道,台积电在其 3nm 工艺良率方面存在困难。消息来源报告的关键传言是台积电发现其 3nm FinFET 工艺很难达到令人满意的良率。但到目前为止,台积电尚未公开承认任何 N3 延迟,相反其声称“正在取得良好进展”。

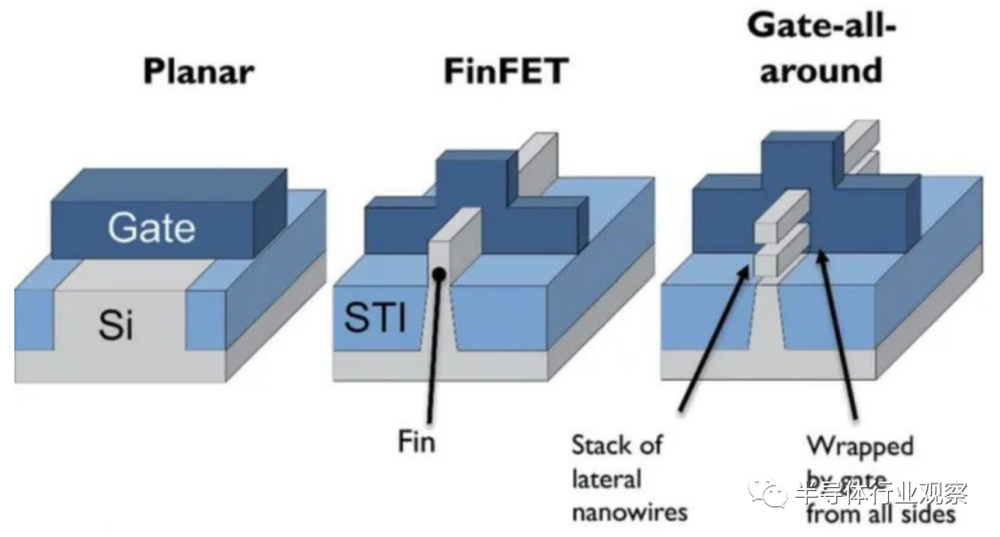

众所周知,台积电3nm在晶体管方面采用鳍式场效应晶体管(FinFET)结构,FinFET运用立体的结构,增加了电路闸极的接触面积,进而让电路更加稳定,同时也达成了半导体制程持续微缩的目标。

其实,FinFET晶体管走在3nm多多少少已是极限了,再向下将会遇到制程微缩而产生的电流控制漏电等物理极限问题,而台积电之所以仍选择其很大部分原因是不用变动太多的生产工具,也能有较具优势的成本结构。特别对于客户来说,既不用有太多设计变化还能降低生产成本,可以说是双赢局面。

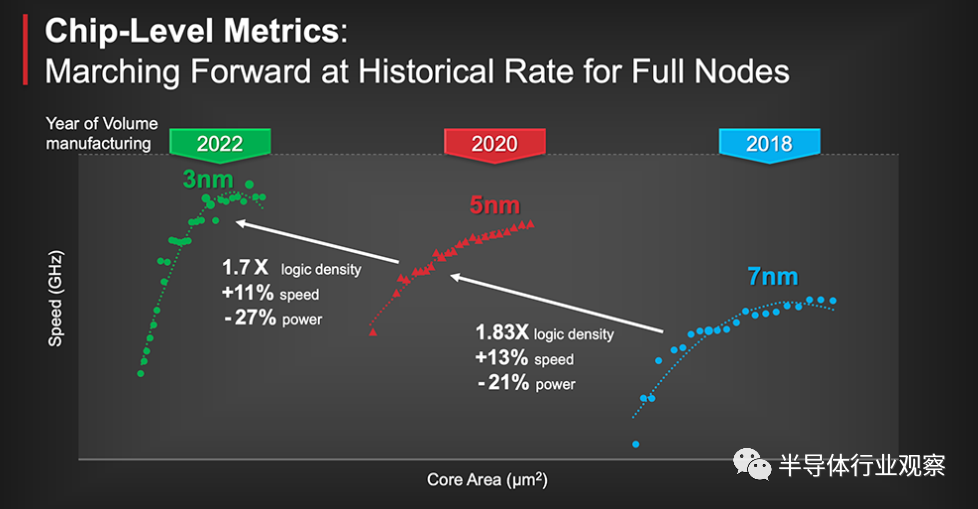

从此前公开数据显示,与5nm芯片相比,台积电3nm芯片的逻辑密度将提高75%,效率提高15%,功耗降低30%。据悉,台积电 3nm 制程已于2021年3 月开始风险性试产并小量交货,预计将在2022年下半年开始商业化生产。

从工厂方面来看,中国台湾南科18厂四至六期是台积电3nm量产基地。客户方面,从上文可以看出,英特尔、苹果、高通等都选择了台积电。大摩分析师Charlie Chan日前发表报告称,台积电在2023年的3nm芯片代工市场上几乎是垄断性的,市场份额接近100%。

三星

不同于台积电在良率方面的问题,三星在3nm的困难是3 纳米GAA 制程建立专利IP 数量方面落后。据南韩媒体报道,三星缺乏3 纳米GAA 制程相关专利,令三星感到不安。

三星在晶体管方面采用的是栅极环绕型(Gate-all-around,GAA)晶体管架构。相比台积电的FinFET晶体管,基于GAA的3nm技术成本肯定较高,但从性能表现上来看,基于GAA架构的晶体管可以提供比FinFET更好的静电特性,满足一定的珊极宽度要求,可以表现为同样工艺下,使用GAA架构可以将芯片尺寸做得更小。

与5nm制造工艺相比,三星的3nm GAA技术的逻辑面积效率提高了35%以上,功耗降低了50%,性能提高了约30%。三星在去年6月正式宣布3nm工艺制程技术已经成功流片。此外,三星还曾宣布将在 2022 年推出 3nm GAA 的早期版本,而其“性能版本”将在 2023 年出货。

目前,在工厂方面,此前有消息称三星可能会在美国投资170亿美元建设3nm芯片生产线。在客户方面,三星未有具体透露,但曾有消息称高通、AMD 等台积电重量级客户都有意导入三星 3nm 制程,但介于上述提到的韩媒报道高通已将其3nm AP处理器的代工订单交给台积电,三星3nm客户仍成谜。

英特尔

在Pat Gelsinger于去年担任英特尔CEO之后,这家曾经在代工领域试水的IDM巨头又重新回到了这个市场。同时,他们还提出了很雄壮的野心。

在本月18日投资人会议上,英特尔CEO Pat Gelsinger再次强调,英特尔2nm制程将在2024年上半年可量产,这个量产时间早于台积电,意味2年后晶圆代工业务与台积电竞争态势会更白热化。

虽然在3nm工艺方面,英特尔没有过多的透露,但是Digitimes去年的研究报告分析了台积电、三星、Intel及IBM四家厂商在相同命名的半导体制程工艺节点上的晶体管密度问题,并对比了各家在10nm、7nm、5nm、3nm及2nm的晶体管密度情况。

报告显示,到了3nm节点,台积电的晶体管密度大约是2.9亿个/mm²,三星只有1.7亿个/mm²,英特尔将达到5.2亿个/mm²。英特尔的晶体管密度比台积电高出了超过79%,达到了三星2倍以上。因此就摩尔定律关注的晶体管密度指标来看,在同一制程工艺节点上,英特尔相比台积电、三星更新一代的制程工艺具有一定的优势。

在工厂方面,英特尔曾强调将斥资800亿欧元在欧洲设厂,英特尔德国负责人Christin Eisenschmid受访时透露,将在欧洲生产2nm或推进更小的芯片。英特尔将2nm作为扩大欧洲生产能力的重要关键,以避免未来在先进技术竞争中落后。

总的来说,在3nm节点,台积电、三星和英特尔谁会是最后的赢家可能只有交给时间来判定,但从目前情势来看,台积电或略胜一筹。

三、3nm后的解法

3nm已经到了摩尔定律的物理极限,往后又该如何发展?这已经成为全球科研人员亟待寻求的解法。目前,研究人员大多试图在晶体管技术、材料方面寻求破解之法。

GAA晶体管

上述三星在3nm制程中使用的GAA晶体管就是3nm后很好的选择,GAA设计通道的四个面周围有栅极,可减少漏电压并改善对通道的控制,这是缩小工艺节点时的关键。据报道,台积电在2nm工艺上也将采用GAA晶体管。

纳米线

纳米线是直径在纳米量级的纳米结构。纳米线技术的基本吸引力之一是它们表现出强大的电学特性,包括由于其有效的一维结构而产生的高电子迁移率。

最近,来自 HZDR 的研究人员宣布,他们已经通过实验证明了长期以来关于张力下纳米线的理论预测。在实验中,研究人员制造了由 GaAs 核心和砷化铟铝壳组成的纳米线。最后,结果表明,研究人员确实可以通过对纳米线施加拉伸应变来提高纳米线的电子迁移率。测量到未应变纳米线和块状 GaAs 的相对迁移率增加约为 30%。研究人员认为,他们可以在具有更大晶格失配的材料中实现更显着的增加。

堆叠叉片式晶体管技术

最近,英特尔一项关于“堆叠叉片式晶体管(stacked forksheet transistors)”的技术专利引起了人们的注意。

英特尔表示,新的晶体管设计最终可以实现3D和垂直堆叠的CMOS架构,与目前最先进的三栅极晶体管相比,该架构允许增加晶体管的数量。在专利里,英特尔描述了纳米带晶体管和锗薄膜的使用,后者将充当电介质隔离墙,在每个垂直堆叠的晶体管层中重复,最终取决于有多少个晶体管被相互堆叠在一起。

据了解,英特尔并不是第一家引用这种制造方法的公司,比利时研究小组Imec在2019年就曾提出这个方法,根据 Imec 的第一个标准单元模拟结果,当应用于 2nm 技术节点时,与传统的纳米片方法相比,该技术可以显着提高晶体管密度。

垂直传输场效应晶体管

垂直传输场效应晶体管(VTFET)由IBM和三星共同公布,旨在取代当前用于当今一些最先进芯片的FinFET技术。新技术将垂直堆叠晶体管,允许电流在晶体管堆叠中上下流动,而不是目前大多数芯片上使用的将晶体管平放在硅表面上,然后电流从一侧流向另一侧。

据 IBM 和三星称,这种设计有两个优点。首先,它将允许绕过许多性能限制,将摩尔定律扩展到 1 纳米阈值之外。同时还可以影响它们之间的接触点,以提高电流并节约能源。他们表示,该设计可能会使性能翻倍,或者减少85%的能源消耗。

其实,对于3nm以后先进制程如何演进,晶体管制造只是解决方案的一部分,芯片设计也至关重要,需要片上互连、组装和封装等对器件和系统性能的影响降至最低。

四、写在最后

关于3nm的争夺,上面只是讲述了冰山一角。其实围绕着整个产业链的每一个环节,几乎都有多家厂商在上面进行争夺。这也正是集成电路发展至今的关键。

另外,虽然摩尔定律已经到了极限,但是无论设计企业还是制造厂又或是封装厂,他们对于先进制程研发的步伐不能停止。往小了说,先进制程关乎产业链的发展,往大了说,先进制程关乎着国家安全。未来世界科技为王,落后就要挨打,这是金规铁律。

本文来自微信公众号:半导体行业观察 (ID:None),作者:龚佳佳