集微网消息,在半导体全产业链中,晶圆制造一直发挥着基础核心作用。目前,随着5G、人工智能和物联网等技术不断发展,各行各业对芯片性能和能效要求越来越高。而推动工艺技术发展的方式主要有两种,一个是芯片尺寸缩微缩,一个是硅片直径增大。由于硅片直径增大涉及整条生产线设备更换,制造工艺精进微缩当前仍是芯片性能持续提升的主要驱动力。

无论如何,只要摩尔定律还存在,半导体巨头势必会抢占先进工艺制高点,其中包括台积电宣布2022年将支出近300亿美元用于2纳米、3纳米等工艺研发;去年三星宣布2022年量产3纳米,2025年量产5纳米;英特尔计划通过2纳米制程重回巅峰;而IBM展示的2纳米制程也着实惊艳了一小阵。同时,欧洲与日本政府及企业也寄望通过2纳米重振芯片制造。

无疑,全球2纳米芯片制程之战的号角已经吹响。但在这场竞逐中,各企业仍主要有“四道坎”需要迈过,包括架构技术、材料、设备和成本。其中,从目前各大厂公布的技术来看,GAAFET全栅场效应晶体管技术将会成为2纳米芯片研制的主流工艺。而二维材料和一维材料有望成为突破2纳米制程研发的潜力材料。此外,满足2纳米研发的光刻机需要2023年开放测试。

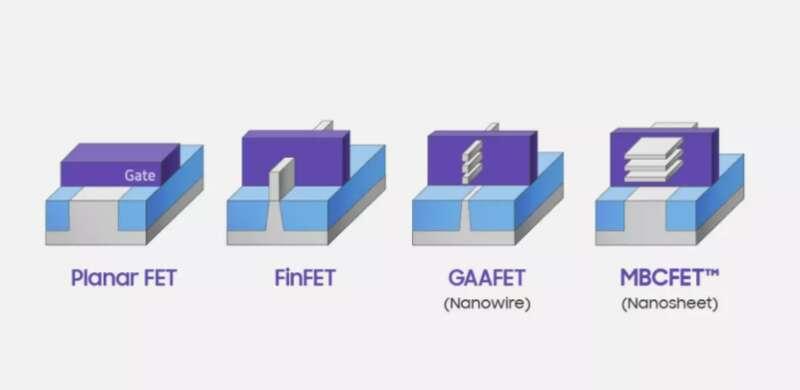

半导体工艺制程晶体管架构示意图

台积电、三星“双雄对决”

作为先进工艺的主力推动者,台积电近年来一直引领行业发展,其中包括2018年推出7纳米,2020年推出5纳米,2022年将如期推出3纳米,同时2纳米工艺也在推进研发,预计最快2024年投产。官方资料显示,与5纳米工艺相比,台积电3纳米的晶体管密度达到每平方毫米2.5亿个,在逻辑密度上提升1.7倍,性能提升11%,同等性能下功耗可降低25%-30%。

为了减少生产工具以及客户设计的变更,台积电的3纳米将会沿用鳍式场效应晶体管(FinFET)架构。但随着工艺节点发展到3纳米后,晶体管沟道进一步缩短,FinFET结构将遭遇量子隧穿效应的限制。因此,台积电据将在2纳米芯片中采用类似全栅场效应晶体管(GAAFET)结构。可以说,这一架构是FinFET技术升级版,将能进一步提升栅极对沟道电流的控制能力。

显然,2纳米在技术上革新非常关键。根据国际器件和系统路线图(IRDS)规划,在2021-2022年以后,FinFET结构将逐步被GAAFET结构所取代。该架构即通过更大的闸极接触面积提升对电晶体导电通道的控制能力,从而降低操作电压、减少疏漏电流,有效降低芯片运算功耗与操作温度。比如GAAFET技术将沟道四侧全部包裹,FinFET的栅极仅包裹沟道三侧。

为了在先进工艺制程上对台积电弯道超车,三星不仅调整了芯片工艺路线图,而且在技术架构上大胆革新,其中包括跳过4纳米工艺,由5纳米直接升至3纳米,而且3纳米、2纳米工艺都将使用GAAFET技术。2021年10月,三星宣布3纳米芯片已开始成功流片,将于2022年上半年生产,第二代3纳米芯片预计于2023年开始生产,2纳米芯片将于2025年量产。

按照规划,三星的3纳米GAAFET工艺将采用多桥式-沟道场效应晶体管(MBCFET)晶体管结构。与当前的5纳米工艺相比,其面积减少35%,性能提高30%,同时功耗降低了50%。此外,在IEDM 2021国际电子元件大会上,三星还携手IBM宣布了一种名为垂直传输场效应晶体管 (VTFET) 的芯片设计技术,并表示该技术突破了目前1纳米工艺设计的瓶颈。

尽管在GAAFET架构的开发时程上落后于三星,但台积电在FinFET技术领域具备深厚底蕴,从而将大大缩短由3纳米FinFET切换至2纳米该技术的周期。按照以往经验,三星在晶体管参数、芯片功耗、发热问题、良品率等性能上都比台积电略逊一筹。此外,作为纯晶圆代工企业,台积电还历来获得了庞大客户群支持。因此,三星的弯道超车梦或依然艰难。

英特尔、IBM“摇旗呐喊”

在经历了先进制程持续“挤牙膏”,移动互联网时代“被超越”以及传统PC市场“被蚕食”后,英特尔希望通过一系列战略举措,重新夺回半导体行业领头羊的地位。而制造能力强化正是其中关键一环。1月22日,英特尔宣布一项新的投资计划,将在美国俄亥俄州投资200亿美元建设两座半导体制造工厂,2025年建成时将使用全球最先进工艺制造芯片产品。

此前,2021年7月,英特尔曾公布了最新的技术路线,并对重要工艺命名进行了修改:10纳米技术改名Intel 7,7纳米技术改为Intel4,5纳米技术改成Intel 3,2纳米技术改成Intel20A。其中,Intel 3在2023年下半年量产,Intel 20A在2024年量产,Intel18A工艺将于2025年推出。而在2纳米节点时,英特尔将由FinFET工艺转向其称为RibbonFET的GAAFET晶体管。

由于先进制程落后竞争对手约一代,英特尔似乎意识到了严峻危机,开始到处求合作,其中包括与三星、IBM签署协议共同研发2纳米工艺,不久后又传出与台积电合作3纳米制程测试。同时,英特尔还在先进工艺研发和制造上大举投资,预计最终将投资达1000亿美元,共建设8家制造工厂。基于此,英特尔未来或将与台积电、三星在先进工艺上展开尖峰对决。

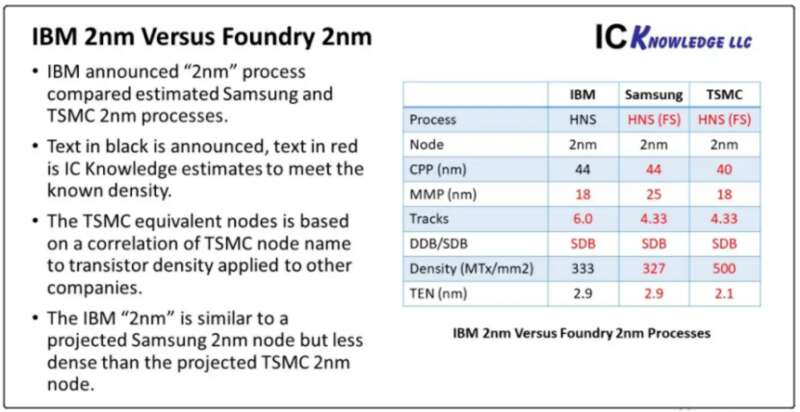

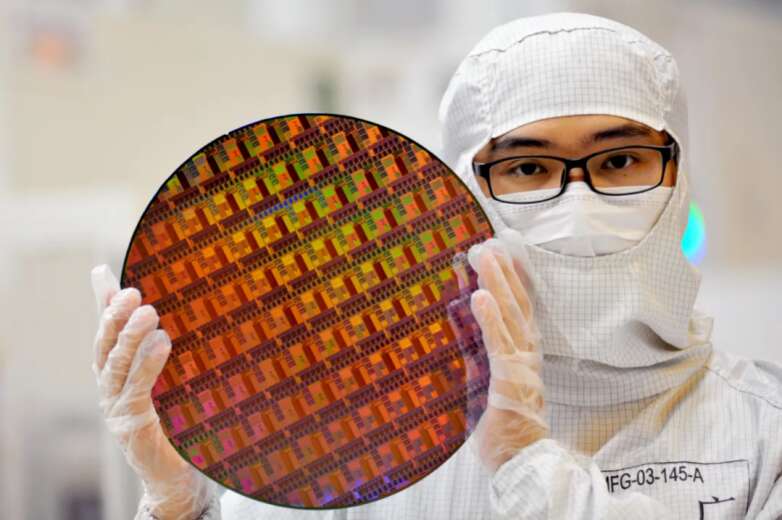

在半导体领域,IBM可谓也是先进工艺制程创新的佼佼者,曾经率先推出7纳米、5纳米乃至2纳米工艺。2021年5月,IBM发布了全球首个2纳米制造工艺,并在美国纽约州奥尔巴尼的工厂展示了2纳米工艺生产的完整300mm晶圆。据预计,IBM 2纳米工艺或能在每平方毫米芯片上集成3.33亿个晶体管,远高于台积电5纳米工艺的每平方毫米约1.71亿个晶体管。

IBM当时宣称,与最先进的7纳米节点芯片相比,这项技术预计可使芯片的性能提升45%,能耗降低75%,并能助力手机、数据中心、PC、自动驾驶等领域应用实现性能飞跃。具体而言,2纳米芯片将加快PC、手机应用程序的处理速度,更快速地接入互联网,以及助力自动驾驶算法更快运行。此外,数据中心能耗巨大,如将处理器替换为2纳米产品将可大大降低等。

不过,虽然同样采用了GAAFET工艺,但该技术目前仍处在概念验证阶段,与量产工艺差距较大。通常,芯片工艺从实验室研发到正式量产商用,还需要代工厂不断提升晶圆良率。而即便解决晶圆良率问题,IBM当前也已不具备大规模量产芯片的能力。此前,IBM曾与三星、英特尔签署了联合研制2纳米的协议,但因需要多方验证测试可能还需几年才能投入市场。

欧洲日本政企“迫切追赶”

尽管在全球半导体产业链中占据极为重要的地位,可欧洲在晶圆制造尤其是先进工艺的实力上并不强。日前,面对美韩等国纷纷强化半导体制造能力,欧洲也再次燃起先进半导体制造的雄心。2021年3月,欧盟委员会发布了《2030数字指南针》计划并提出新的目标,到2030年欧洲先进和可持续半导体的生产总值至少占全球生产总值的20%,生产能力冲刺2纳米。

显而易见,欧洲半导体研究历史悠久、产业链各环节基础扎实、科研机构实力强劲。但与强大的设计、研发实力相比,欧洲在晶圆制造尤其先进工艺上的实力相对薄弱,甚至没有一家代工企业入围全球前十。多年来,英飞凌、恩智浦和意法半导体等企业专注于汽车电子、工业产业等稳健领域,但却错过了存储器、晶圆代工和智能手机芯片等需要先进工艺的热门领域。

受供应短缺、贸易摩擦和经济不振等多重因素影响,日本也有意强化本国先进工艺芯片的制造能力。2021年3月,日本政府宣布将出资420亿日元,联合日本三大半导体厂商——佳能、东京电子以及Screen Semiconductor Solutions共同开发2nm先进工艺制程。此外,日本官方还推动与台积电、英特尔等头部大厂建立合作关系,以寻求收复在全球半导体竞赛中的失地。

事实上,日本对先进晶圆制造领域的布局早有迹可循。2020年5月,有关日本政府邀请国外芯片制造商赴日建设晶圆工厂的消息就屡屡传出,可台积电后来决定去美国建设先进工艺晶圆代工厂。虽然晶圆制造“外援计划”落空,但日本仍然没有放弃,转而向先进封装等领域发起攻势。最终,台积电宣布将在东京先进封测厂,并在筑波市设立晶圆及3D封装研发中心。

无疑,晶圆制造涉及庞大的资本支出和各项复杂技术。于是,2022年初,日本政府半导体产业咨询组官员表示,日本应该提供租税减免优惠,以便在未来十年内达到产能880亿美元的投资效益。同时,日本必须在十年内实现2纳米制程量产。基于财政优惠或补贴、半导体材料领域积累、本土产业链企业携手以及外援协助,日本欲重振芯片制造的长路或将更有底气。

点评:2纳米要过“四道坎”

无论是结构上的创新还是新材料的引入,2纳米都将是一个非常关键的节点。原有的多项技术难以满足发展要求,产业界需要从器件架构、工艺变异、热效应、设备与材料等方面综合解决。而在这条具备新机遇的赛道上,欧美、日韩等国的企业均已将芯片制造的突破重点放在2纳米上。但想要突破并不容易,2纳米芯片制造在架构、材料和设备等方面仍面临多重瓶颈。

首先,目前2纳米制程技术关注的重点在于晶体管架构将由FinFET进入GAAFET世代。相比FinFET,GAAFET架构为四面环绕式包覆,更能有效提高效能同时控制漏电等,因而或将成为2纳米工艺的主流架构。因此,对各企业而言,熟练掌握GAAFET技术至关重要。但目前,仅有三星在2纳米上迭代为第二代GAAFET架构制程,台积电等厂商仍处在规划状态。

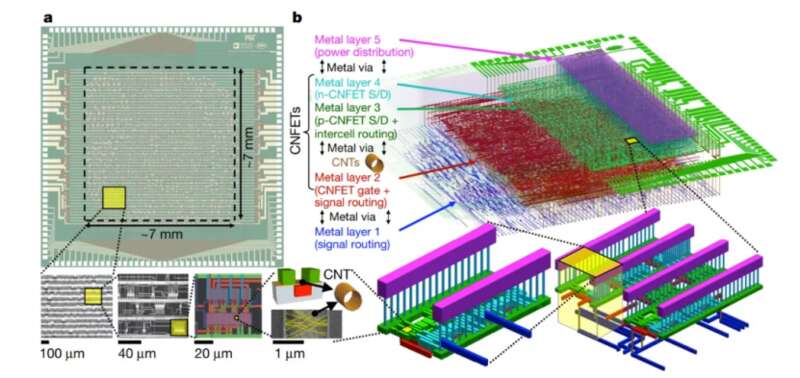

其次,对于2纳米工艺研发,新型材料的选择与应用同样会起到至关重要的作用。据了解,二维材料及其范德华异质结电子学器件,已在超低功耗晶体管、超快逻辑运算、光电互联及新型高密度存储等领域表现出极大发展潜力,将在未来助力突破2纳米以下先进制程研发。具体而言,石墨烯、碳纳米管、过渡金属化合物等二维或一维材料因尺寸较小有望替代硅基材料。

碳纳米管基芯片 图源:Nature

另外,制造2纳米工艺还需要光刻机等设备支撑。据公开信息,ASML正在研发High NA(高数值孔径)EUV光刻机,可满足2纳米的研发和生产需求。其首台High NA EUV光刻机将于2023年开放早期测试,并从2025年开始量产。具体来看,满足2纳米制程生产需求的光刻机,还需要突破革新光学分辨率、光刻胶等相关技术和设备系列问题,因而“道阻且长”。

再者,来自制造成本方面的挑战更加严峻。数据显示,7nm工艺仅研发费用就至少需要3亿美元,5nm工艺平均要5.42亿美元,而3nm、2nm的工艺起步价大约在10亿美元左右。目前,台积电3nm工艺的总投资约为500亿美元,在建厂方面至少已经花费200亿美元,可见投入之庞大。如果一旦投入,相关企业势必将面临用户从哪里来,如何平衡生产成本等问题。

毫无疑问,先进制程技术的推出对于集成电路产业和市场格局有重大意义,而研发迟滞的半导体厂商必将被其他厂商的先进制程所超越甚至替代。当前,虽然2纳米工艺还有技术架构、材料、设备和成本等不少难点需要克服,但各巨头的涌入竞争,将可以为整个集成电路行业和用户带来不菲益处。由于工艺技术研发充满变数,未来谁能最终脱颖而出还需进一步观察。