本文来自微信公众号:半导体行业观察(ID:icbank),作者:龚佳佳,头图来自:unsplash

被半导体产业奉为圭臬的“摩尔定律”即将迈入第57个年头,同时,它也将进入“将死”的又一年。自1965年,摩尔定律首次被提出来以后,全球芯片技术基本都是在这原理下运行,它见证了人类信息技术前进的脚步。

回顾过去,从本世纪初开始,就不断有业界大佬预测摩尔定律“将死”。2004年国际半导体技术发展路线图(ITRS)修订版就预测,摩尔定律这种线性发展可能继续保持10年~15年。

2013年,美国国防部先进研究项目局认为,2020年,7纳米将是芯片的最后制程节点。其微系统技术办公室主管罗伯特·克罗韦尔表示,预计芯片产业会花大工夫推进5纳米制程,这会将摩尔定律最初的终结时间推迟到2022年。2015年,博通首席技术官Henry Samueli表示:“摩尔定律已经头发花白,步履蹒跚了。它还没死,但是时候退休了。”

在“摩尔定律将死”的无形之剑下,全球半导体产业经历了一年又一年,到如今芯片制程节点已经冲刺3nm。而全球研究人员也“头顶悬剑”,不断地开拓新材料、新晶体管、新设备等领域,以此来迎接未来芯片的挑战。

一、二维材料有望变革传统集成电路架构

众所周知,晶圆的原始材料是硅,硅作为一种半导体可以通过引入少量杂质的方法,调节为良好的导体或者绝缘体。然而,随着近年来集成电路的制程进入5nm以下,晶体管的尺寸不断缩小逼近其物理极限,传统的硅基材料越来越难以支撑集成电路性能的进一步发展。

二维材料是一种从2004年发展起来的新材料,以过渡金属硫族化合物(TMDC)为代表,包括通式为MX2的过渡金属二卤化物(TMD),其中M为过渡金属(例如,Mo或W),X为硫族元素(例如S、Se或Te)。这种材料具有极限厚度、高迁移率和后端异质集成等特点,将有望变革传统集成电路的架构,受到了学术界和工业界的关注。

目前,英特尔、三星、台积电等处于芯片技术前沿的大厂们都已布局这个领域。为了应对未来芯片危机,欧洲也致力于石墨烯等二维材料研发。此外,我国北京大学、南京大学等也在这个领域取得了技术突破。

英特尔:MoS₂解决传统硅芯片的物理限制

近日,在2021 IEEE国际电子器件会议(IEDM)上,英特尔公布了突破摩尔定律的三种新技术,这些技术的目标是在2025年之后还能使芯片技术继续发展,而其中就提及了二维材料。

据了解,英特尔提出用一种叫做TMD(过渡金属硫化物)的二维材料代替硅成为电流通道,特点是在通道下面,有一层非常薄的,单层的二硫化物原子层,可以作为更短的通道。

英特尔制造、供应链和营运集团副总裁、战略规划部联席总经理卢东晖指出,“硅的问题是无法继续往下缩,再往下缩会出现很多量子效应,但二维材料有自己本身的特质,所以可以做得非常小。”英特尔在材料上最大的突破是用两种不同的金属去做金属接触,NMOS用的是锑,PMOS用的是钌,这样能让电容更小。

英特尔表示将单层二硫化钼MoS₂应用于硅芯片连接层可以使得间距从15nm缩小至5nm,解决传统硅芯片的物理限制。

台积电:MoS2结合铋实现极低接触电阻

而台积电则是联手台湾大学、麻省理工学院发现了二维材料结合半金属铋可以实现极低的接触电阻,接近量子极限,这一研究发现于今年5月发表于自然期刊。

据了解,受到高电阻与低电流的限制,石墨烯等二维材料一直无法取代硅基半导体。麻省理工团队首先发现二硫化钼(MoS2)与半金属铋结合可以有效降低电阻,提升电流的传输效率。台积电技术研究部门随后对铋沉积制程进行了优化,最后台大团队利用氦离子束微影系统将元件通道成功缩小至纳米级,才得出这一研究成果。

早在去年3月,台积电就曾与台湾交通大学联合研制的最薄氮化硼二维绝缘材料,该材料厚度仅为0.7nm,可以用于1nm制程的突破。

三星:发现新材料“非晶态氮化硼”

去年7月,三星电子技术学院表示,他们与蔚山科技学院合作,成功发现了新材料“非晶氮化硼(a-BN)”。据介绍,研究小组不仅确保了世界上最低1.78的介电常数,而且还证明了该材料可以在400°C环境下,在半导体基板上大面积生成,从而朝着工艺创新迈出了一步。非晶氮化硼可应用于包括存储器半导体(DRAM、NAND等)的半导体系统,并且有望用于要求高性能的服务器用内存半导体。

其实三星对二维材料的研究已进行了多年。2012年,三星使用石墨烯开发新的晶体管结构;2014年,三星解决了石墨烯半导体晶片上无法生成的限制,在晶片上形成了世界上第一层纯石墨烯层,并开发了用于大规模生产的源技术;2017年:三星摆脱现有石墨烯的规则六边形网格结构,碳原子以无规形式连接的石墨烯结构开发,大面积成功合成。

欧盟:致力二维材料研发

为了应对未来芯片危机,欧洲也致力于石墨烯等二维材料研发。早在2013年,欧盟就投资了10亿欧元,以推动之后10年内的石墨烯技术发展。最近一年来,石墨烯材料的3条试验生产线已经投入运行。

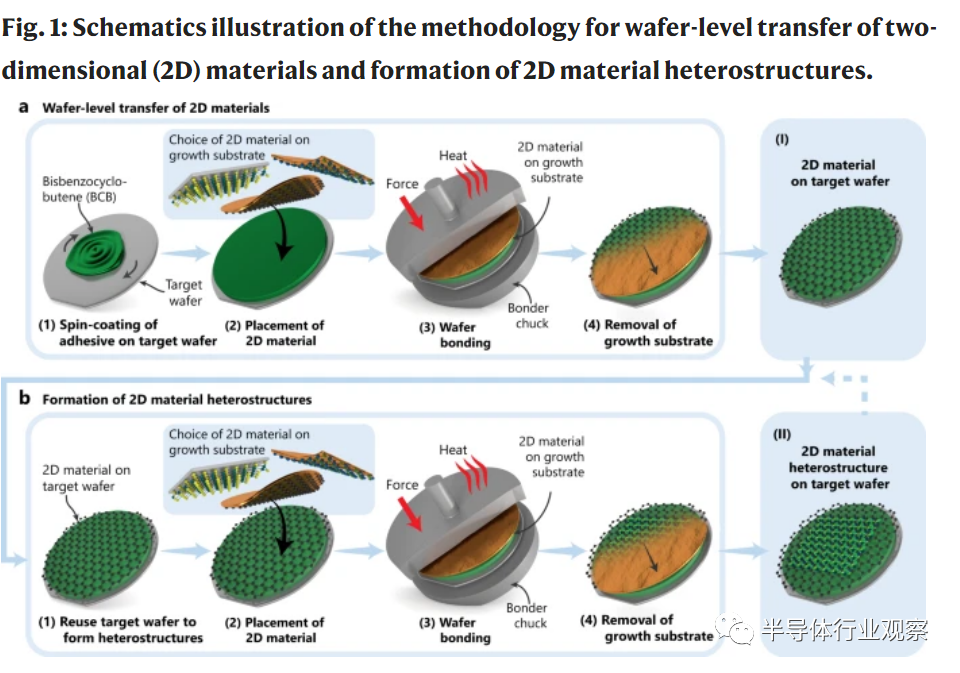

今年年初,欧盟“石墨烯旗舰计划”的一项最新实验,提出了一种将石墨烯和2D材料集成到半导体生产线的新方法,并发表在《自然·通讯》上。

研究人员采用直径100mm的铜箔作为化学气相沉积(CVD)制单层石墨烯的生长基底、采用直径为1cm的带氧化层硅片(SiO2/Si)作为二硫化钼的生长基底,并将这两种材料转移至直径100mm的硅基底上,提升二维材料转移成功率。

北京大学:实现2英寸单层单晶WS2的外延制备

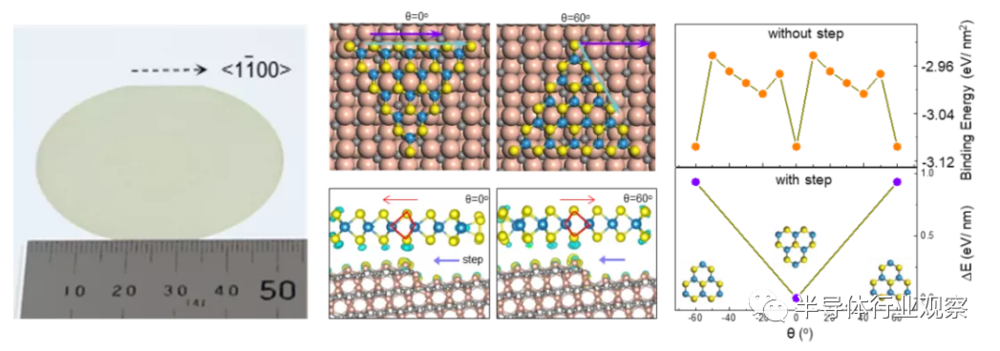

11月15日,松山湖材料实验室/北京大学刘开辉研究员、王恩哥院士团队与合作者,在Nature Nanotechnology上发表了题为“Dual-coupling-guided epitaxial growth of wafer-scale single-crystal WS2 monolayer on vicinal a-plane sapphire”的研究论文,首次提出“双耦合协同调控”的全新生长机理,成功在蓝宝石衬底上实现了2英寸单层单晶二硫化钨(WS2)制备。

研究团队经过深入探索,提出二维材料与绝缘衬底面内范德华耦合作用和台阶相互作用的“双耦合协同调控”新机理,实现了2英寸单层单晶WS2的外延制备。“双耦合协同调控”机理的关键物理思想在于:WS2和蓝宝石衬底间的范德华相互作用将WS2晶畴的优势取向限制为0°与180°;WS2和蓝宝石台阶间的相互作用可以打破2个取向的能量简并性,从而使WS2晶畴只保留1个优势取向。

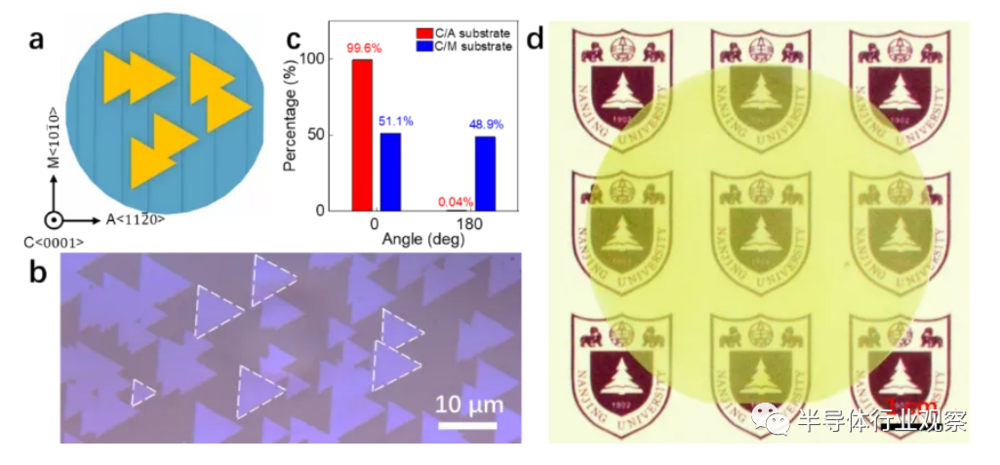

南京大学:实现2英寸MoS2单晶薄膜外延生长

南京大学电子科学与工程学院王欣然教授课题组通过改变蓝宝石表面原子台阶的方向,人工构筑了原子尺度的“梯田”。利用“原子梯田”的定向诱导成核机制,实现了TMDC的定向生长。基于此原理,团队在国际上首次实现了2英寸MoS2单晶薄膜的外延生长。

得益于材料质量的提升,基于MoS2单晶制备的场效应晶体管迁移率高达102.6 cm2/Vs,电流密度达到450 μA/μm,是国际上报道的最高综合性能之一。同时,该技术具有良好的普适性,适用于MoSe2等其他材料的单晶制备,该工作为TMDC在集成电路领域的应用奠定了材料基础。

二、晶体管结构新变革

随着工艺一步步演进,晶体管的尺寸也在一点点缩小,以便在给定的芯片面积内集成更多的电子元件,从而带来更强的系统功能和更低的指数级成本。但如今,“摩尔定律”即将迎来其57“大寿”,芯片制程也迈入了后FinFET时代,可以塞进单个芯片的晶体管数量几乎达到了极限。毋庸置疑,除了新材料外,晶体管结构也将迎来新变革。

GAA

在上述英特尔公布的突破摩尔定律三种新技术中,晶体管微缩面积的提升也是其中之一。据悉,英特尔将采用GAA RibbonFET(Gate-All-Around RibbonFET)技术,通过堆叠多个(CMOS)晶体管,实现高达30%至50%的逻辑微缩提升,单位面积的晶体管数量越多,半导体的性能也就越强大。RibbonFET是英特尔对于GAA晶体管的实现,也是公司自2011年率先推出FinFET以来的首个全新晶体管架构。

与FinFET的不同之处在于,GAA设计通道的四个面周围有栅极,可减少漏电压并改善对通道的控制,这是缩小工艺节点时的关键。三星此前也宣布将GAA用于3nm工艺,预计于2022年投产。此外,台积电董事长刘德音也曾指出,在2nm之后,台积电将转向采用GAA的架构,提供比FinFET架构更多的静电控制,改善芯片整体功耗。

VTFET

在2021 IEDM上,IBM和三星公布了一种在芯片上垂直堆叠晶体管的新设计,即VTFET。VTFET(垂直传输场效应晶体管)将晶体管垂直于硅晶圆,并引导电流垂直于硅片表面。这种新方法通过打破对晶体管栅极长度、间隔厚度(spacer thickness)和触点尺寸的物理限制来解决缩放障碍,以便优化包括性能和功耗在内的各种参数。

根据IBM和三星的说法,这种设计有两个优点。首先,它将使他们能够绕过许多性能限制,使摩尔定律超越IBM目前的纳米片技术。更重要的是,由于更大的电流流动,这种设计导致了更少的能量浪费。他们估计,VTFET将使处理器的速度比使用FinFET晶体管设计的芯片快一倍,或减少85%的功率。

待VTFET技术成熟,已宣布采用GAA技术的三星,未来是否会将VTFET用于先进制程,我们也拭目以待。

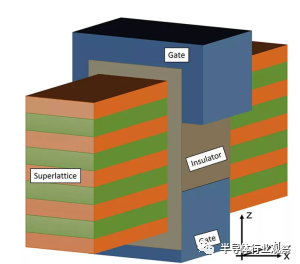

CasFET

CasFET是由普渡大学工程师推出的新型晶体管,具有垂直于晶体管传输方向的超晶格结构,它们的行为类似于量子级联激光器,而不是传统的 FET 器件,从而让晶体管实现开关电压更低、功耗更低、设计更密集,体积更小。

普渡大学电气和计算机工程助理教授蒂尔曼·库比斯(Tillmann Kubis)指出,“模拟量子级联激光器通过外部电场转换其传输性质,从相干/弹道传输到逐步和声子辅助隧道传输。这种开关效应是我们添加到 FET 的“标准”场效应开关中的。

此外,他还补充道,“与最先进的晶体管相比,CasFET对栅极更敏感,这也适用于栅极全能 FET。所有这些晶体管都依赖于单一的开关机制。我们的有两个。”目前原型 CasFET 设备还在设计中。

三、下一代EUV光刻机也要做好准备

提到未来芯片工艺制程,光刻机显然是必不可缺的话题,可以说,制程突破在一定程度上受制于光刻机。光刻的本质其实是一个投影系统,光线被投射通过掩模版,成像在晶圆上,最终在晶圆上一层一层建立起复杂的晶体管。随着光刻技术不断朝着“更小”征程迈进,下一代光刻机也需要做好充足的准备。

High-NA EUV

为了避免 EUV 双重图案化,High-NA EUV成为了焦点,其可以实现更简单的单图案方法。光刻机巨头ASML 将通过重新设计光刻系统内的光学器件,从目前的 0.33 NA 变为 0.55NA(即 NA 增加 67%)。0.55NA EUV 光刻有望最终实现 8nm 分辨率,对应于一次曝光中 16nm 间距的印刷线/间距。

根据ASML 的10月分享报告显示,其最新的 EUV 光刻机可以在未来 10 年左右的时间内帮助制造商在硅基板上塞入越来越多的晶体管。根据ASML预测,到2030年,将会有集成3000亿晶体管的芯片出现。

ASML报告指出,从 2023 年开始,ASML计划交付第一批下一代 EUV 设备,该设备将从 0.33 NA 到 0.55 NA,使 EUV 数值孔径(NA)高于当前机器的能力。而这可以让芯片制造商开发出远远超过当前预期的 2 nm阈值的工艺节点,并且在对高级晶圆层使用单次曝光 EUV 工艺时还可以节省一些成本。

EUV 光刻胶

未来工艺节点向high NA光刻的过渡不仅需要来自ASML等系统供应商的工程创新,还需要对合适的光刻胶材料进行高级开发,不断提高光刻胶的性能。

Lam Research 将使用化学气相沉积工艺在金属光刻胶上分层,而不是湿式光刻胶(wet photoresist )技术。Lam Research 干式抗蚀剂技术的最大优势之一是使用化学气相沉积(CVD)工艺来沉积光刻胶,从而可以更精细地控制光刻胶的可变性和厚度。

东京电子发现了一种新的溶剂冲洗工艺,可以将生产线扩展到 ~24nm(12nm 临界尺寸)。这个工艺或将允许湿抗蚀剂方法缩放到 24 nm。

TokyoElectron 和 JSR 声称他们有一种新的金属氧化物抗蚀剂曝光后烘烤工艺,这将有助于提高光刻胶的灵敏度。

新掩膜类型

除了光刻胶外,High-NA EUV 还需要新的光掩模类型。为了减少不必要的图案放置偏移产生的影响,EUV 掩模需要更薄的吸收剂。当前EUV 掩模中,钽吸收剂的厚度为 60nm,虽然它可以做得更薄,但被限制在50nm,并不能解决掩膜效应。为此,业界正在开发几种新的 EUV 掩模类型,例如 2D、无吸收体、高 k、非反射和 PSM。

在 SPIE Photomask/EUV 会议上的演讲中,汉阳大学的研究人员描述了一种相移 EUV 掩模,它由基板上的钌和硅交替层组成。钌覆盖层位于多层结构的顶部,然后是钽-硼蚀刻停止层,以及作为相移材料的钌合金。

High k 掩模在研发中,业内正在探索镍等其他材料替代钽吸收剂。据了解,更薄的镍吸收剂可以减轻掩模效应,但同时也很难使用。

此外,初创公司 Astrileux 也描述了一种使用钌材料的新型非反射 EUV 掩模。这家公司还表示,2D 掩膜等都在研发中。

五、写在最后

技术或许有极限,但人类的智慧没有极限。“摩尔定律”何时会死去,没人会知道,但随着研发人员不断地探索,或许它将会被源源不断地“续命”,未来芯片危机也或许会在某一天伴随着某个新技术的诞生迎刃而解。

最后引用硅谷王川在《为什么摩尔定律一直没死, 但人们还会继续预测摩尔定律要死》中的一段话,“就是更多钱,更多人,更好的工具,更快的通讯,多个提高晶体管密度的解决方案齐头并进,这些解决方案中冒头的最佳方案,肯定会不断超越以前的解决方案的效率。但是在那个赢家冒头之前,我们很难提前预测哪个方案会胜出。”

本文来自微信公众号:半导体行业观察(ID:icbank),作者:龚佳佳