本文来自微信公众号:半导体行业观察(ID:icbank),作者:Dylan Patel,编译自semianalysis,头图来源:视觉中国

通过在光刻图案的分辨率上提供阶跃函数增加的保真度,EUV光刻从根本上推动了半导体行业向前发展。然而,分辨率的提高并不是免费的。许多伴随的进步也不得不带来多个方面的变化,进而导致EUV 成本的提升。这些变化包括掩模生产、薄膜、沉积、蚀刻、硬掩模和光刻胶。虽然 EUV 本身由 ASML 主导,但这种转变已经在制造过程中的相邻步骤(尤其是光刻胶行业)引发了一场价值数十亿美元的高风险战斗。

日本长期以来一直在该领域占据主导地位,东京电子拥有 EUV 光刻胶涂布机和显影剂(photoresist coaters 和developers) 100% 的份额。由于他们在这个领域的垄断地位,这让他们在该市场以及蚀刻和清洁方面相关领域取得的年收入高达 50 亿美元!此外,其他日本公司早已以约 75% 的市场份额垄断了光刻胶市场。JSR 和 Tokyo Ohka Kogyo就是其中的领先者。他们提供了绝大多数专门用于 EUV 的化学放大(chemically amplified photoresist )光刻胶。然而,这些市场正受到 Lam Research 的冲击。

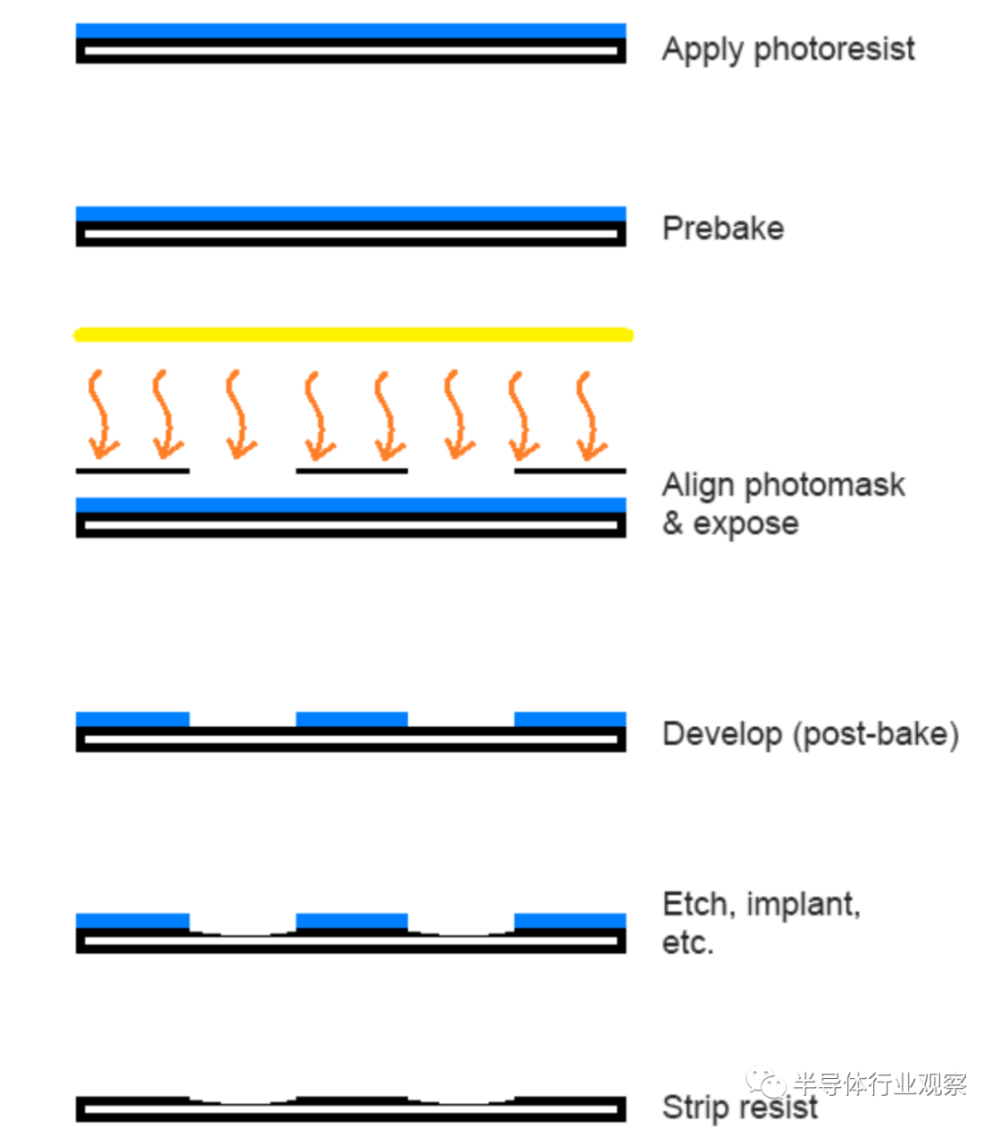

在深入探讨即将到来的光刻胶战争的细节之前,让我们简单概述一下光刻图案化过程。这一切都从清洁晶圆开始,这个步骤是为了确保晶圆上没有异物,如微小的灰尘分子或先前工艺中的残留化学品。

在更高级的节点中,在光刻工艺之前,会有一些底层、中间层和硬掩模沉积在晶圆上。完成此沉积是为了更准确地控制最终蚀刻,这是另一个话题。

最简单的光刻形式将称为使用湿光刻胶(wet photoresist)的单一图案化。清洗后的晶圆被放入东京电子涂布机和显影剂中。该工具在硅片顶部沉积化学放大抗蚀剂 (CAR)。CAR 悬浮在液体溶液中,硅片以极快的速度旋转以涂覆硅片。旋转过程还通过离心力去除大部分液体,并留下一层薄薄的光刻胶。还进行了称为预烘烤的过程,以烤干最后一点液体,并在某些情况下以化学方式为即将进行的反应准备光刻胶。

随后,硅片进入 ASML的光刻工具,然后通过掩模将光线照射到光刻胶上,并在那里引起化学反应。之后,晶圆被送回到东京电子涂布机/显影工具清洗,使用显影剂洗掉光刻胶。如果这种光刻胶是正性的,那么曝光的光刻胶会发生反应并变成溶剂,这样它就可以被洗掉。如果是负的,曝光的光刻胶反应不再是溶剂,未曝光的光刻胶被洗掉。这仅适用于光刻工艺,除此之外还存在其他相关工艺,例如多图案技术、蚀刻和间隔物,但让我们今天关注光刻工艺。

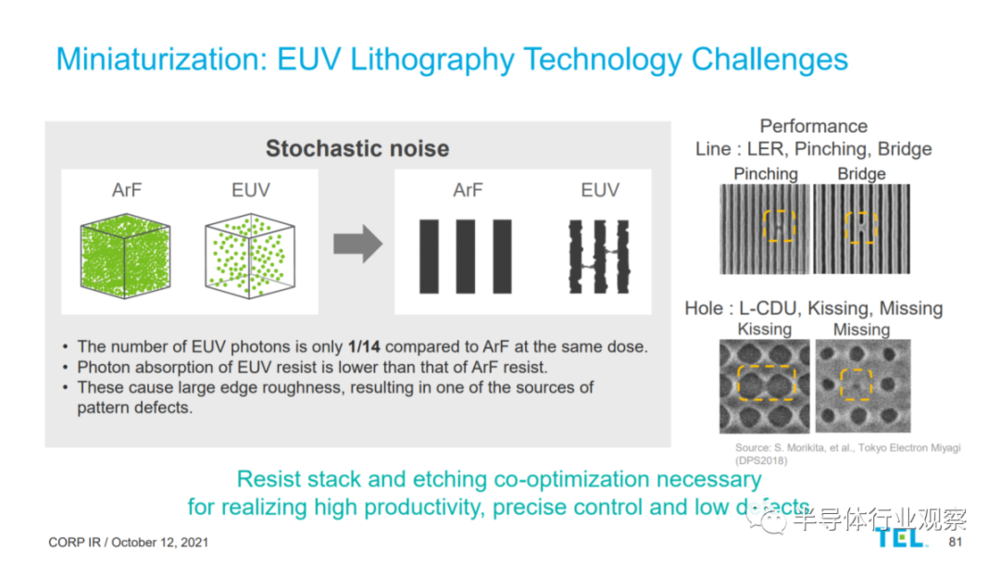

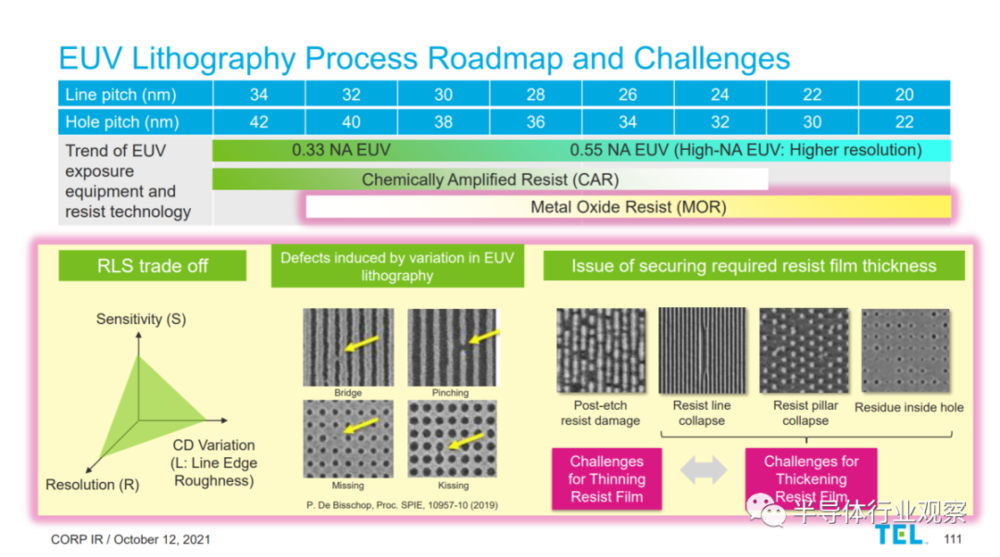

上面概述的光刻胶工艺已经出色地工作了几十年,但它开始遇到重大问题。这与线边缘粗糙度、灵敏度、分辨率和吞吐量有关。EUV 光刻使用相对于 DUV 而言极短波长的光来轰击晶圆。较短波长的极紫外光的生成难度要大得多。

EUV 存在吞吐量问题。这个问题主要围绕一个事实,即相对于DUV,EUV光刻机只有1/14剂量的光子打在晶圆上。因此,必须增加 EUV 中的剂量,这反过来又通过增加曝光时间来降低吞吐量。产能问题导致晶圆产量受到严重限制,成本增加。为了最大化吞吐量,剂量被最小化,这会导致与特征保真度相关的各种问题。

一种解决方案是使用更多的机器并从光源上入手,然而EUV光刻机机器极其昂贵,每台约 1.5 亿美元,而且ASML 的产量非常有限。至于增加光源功率,也相当非常困难,ASML 的功率增加路线图远不及 EUV 层在新节点上增加的速度。

除了更少的光子暴露在光刻胶上之外,EUV 光刻胶也吸收更少的光子。这主要因为光刻胶溶液是光酸产生剂、粘合促进剂和稳定剂的极其精确的混合物。那就意味着如果在过程中出现差错,会是一个代价高昂的错误。2019 年,台积电的 Fab 14B 光刻胶出现问题,最终给他们带来高达5.5 亿美元的损失。使用 EUV 光刻胶,这种平衡行为更加难以控制,因为特定的混合物会导致吸收更少。对 EUV 的需求以及 1~2 次更少光子和更少吸收的需求相结合,为经典光刻胶行业提供了一个成熟的机会。这就吸引厂商进入干燥抗蚀剂(dry resist)市场。

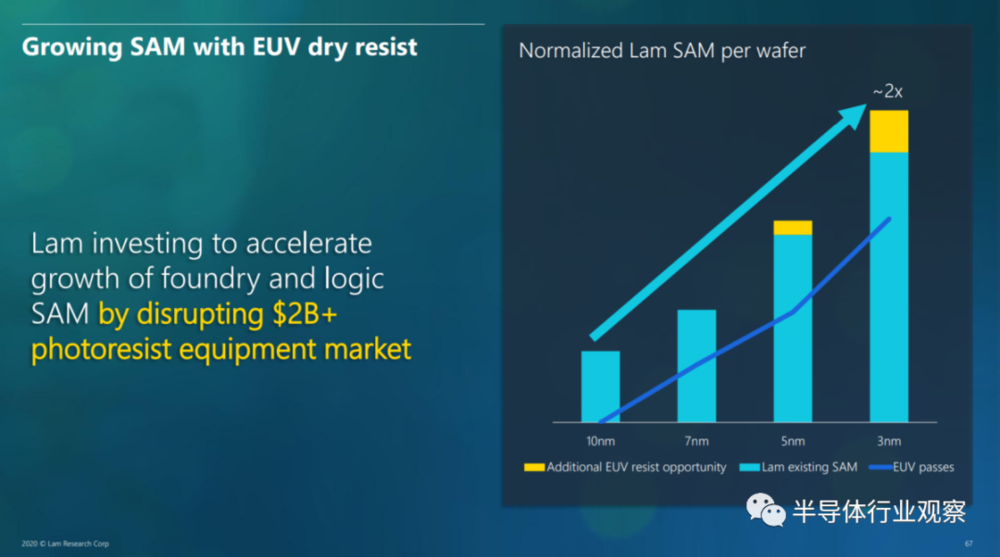

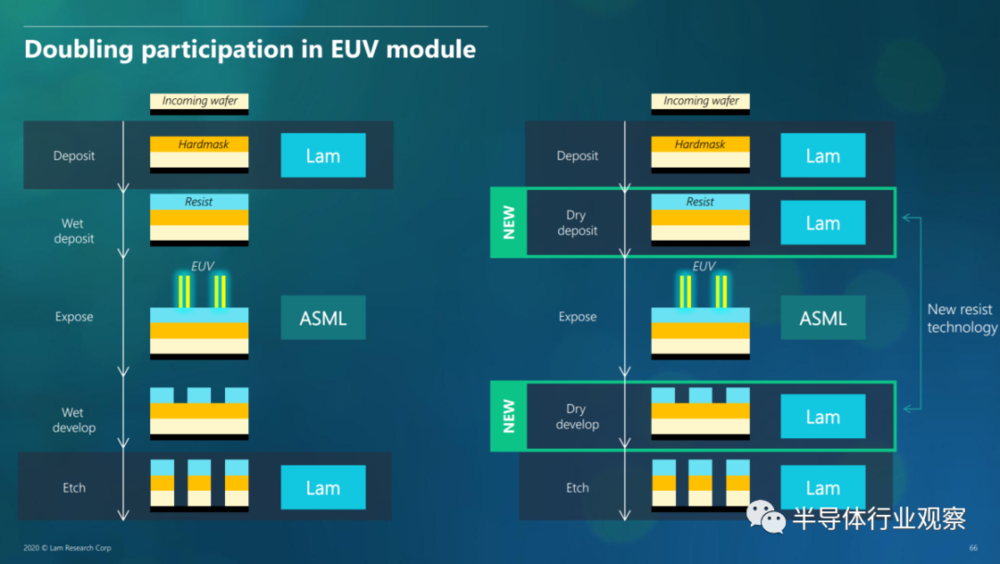

Lam Research 正试图成为当中的搅局者。他们将使用化学气相沉积工艺在金属光刻胶上分层,而不是使用旋涂机的湿式光刻胶(wet photoresist )技术。Lam Research声称干式光刻胶技术(dryresist )与湿式光刻胶相比具有多项优势。由于是一种密集沉积的金属(metal),它不会与许多其他化学物质混合。这允许金属光刻胶仅作为吸收剂。回到吞吐量,这意味着每个晶圆通过和功率降低了 2 倍。每台 EUV 工具吞吐量几乎翻倍,这将大大降低成本。

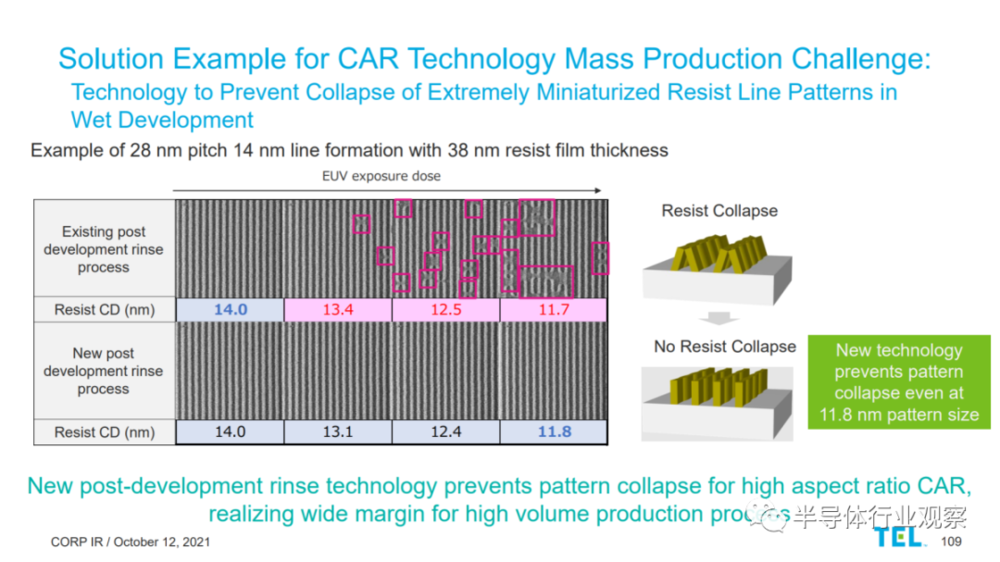

灵敏度并不是唯一的优势。Lam 的干式光刻胶也是采用干法开发的。在湿显影中,光刻胶用水或酸洗涤。当光刻胶由于毛细作用力溶解掉时,图案化的线条和其他特征可能会坍塌。随着最小金属间距 (MMP) 超过 28 纳米,这越来越成为一个问题。台积电的 N5 和 N4 工艺节点的 MMP 分别为 30nm 和 28nm,因此当前的出货节点正好处于边缘。

然而,东京电子仍有创新在进行中。虽然他们同意现有的开发冲洗工艺确实会导致超过 28nm 间距(14nm 临界尺寸)的生产线塌陷,但他们发现了一种新的溶剂冲洗工艺,可以将其扩展到 ~24nm(12nm 临界尺寸)。这将允许将湿抗蚀剂方法缩放到 24 纳米。

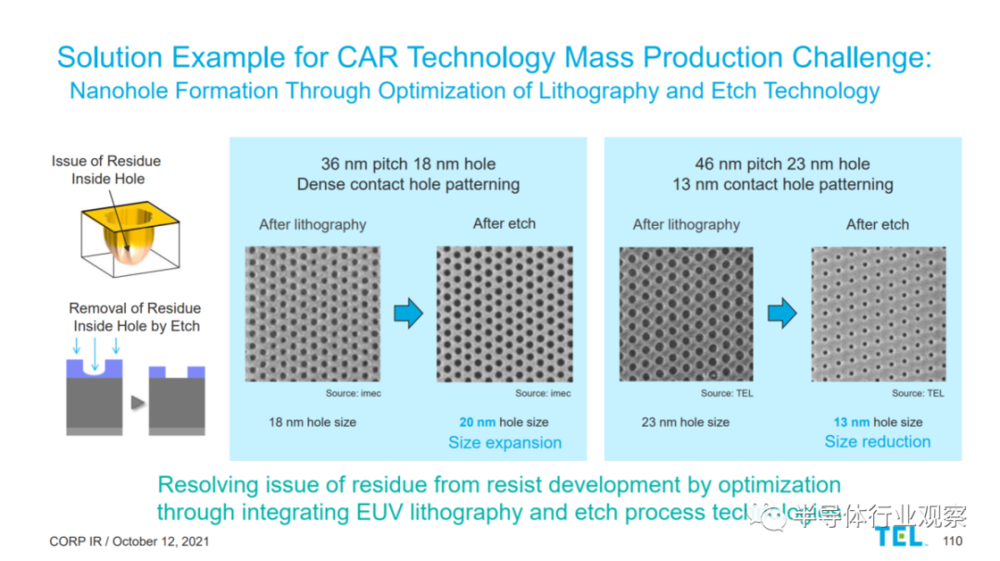

但并不是湿抗蚀剂的所有问题都解决了,因为我们还是很难洗掉所有的光刻胶。如果所有的光刻胶没有被洗掉,以后的步骤就会有问题。残留的光刻胶在蚀刻时会导致孔洞,最终相互“亲吻”。残留物也可能导致这些孔完全丢失。

东京电子目前对此的解决方案是简单地蚀刻残留的光刻胶。虽然这是一个简单的解决方案,但可能会出现复杂情况,因为它会导致孔变大或倾斜。斜面效果不一定是负面的,但也不是在所有用例中都是最佳的。

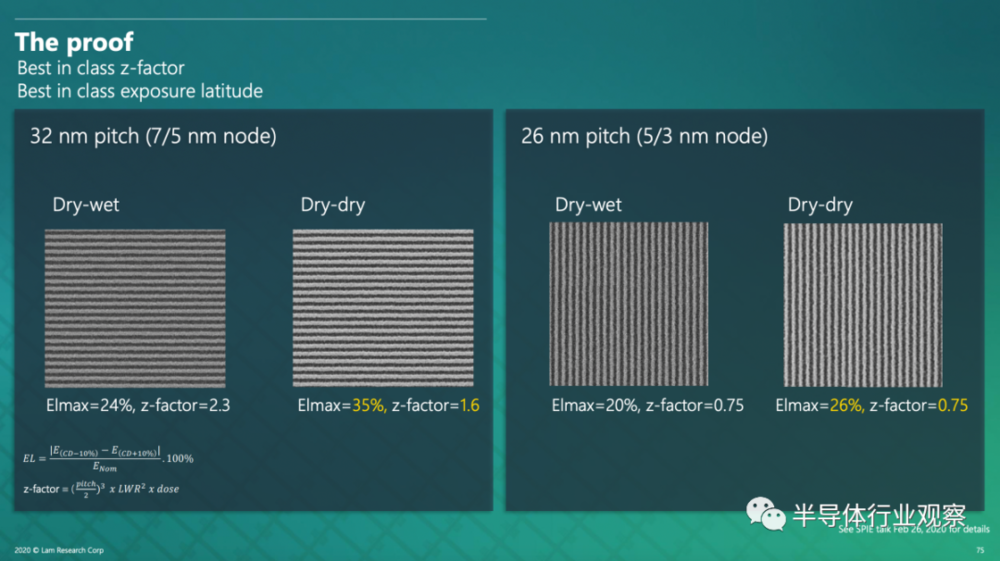

Lam Research 声称他们的工艺可以实现 5nm 节点上使用的现有 32nm 间距,与现有的湿式光刻胶工艺相比,其方案具有更低的可变性和更好的宽容度。我们无法与 Lam Research 分享的硬性数字进行争论。当晶圆厂追求特征尺寸、性能和功耗时,干法工艺总体上更好。由于显示了当前部署的工具和流程与即将推出的工具和流程,因此 Lam Research 进行的比较可能被认为是不诚实的。

与此同时,东京电子正在尽最大努力延长现有产品的寿命。他们的Clean Track Lithius Pro Z 与每台 ASML EUV 机器一起使用。事实证明,它对于最初的 EUV 节点是可靠且高效的,但随着行业超越单一图案化 EUV,化学放大抗蚀剂 (CAR) 显然已达到极限。在其他条件相同的情况下,干式抗蚀剂将在前沿和最小特征尺寸方面获胜。

Lam Research 最初的目标是在 5nm IMEC 节点(代工厂为 3nm)上使用。他们与 IMEC 和ASML 合作进一步开发这项技术。Lam 还与三星、英特尔、台积电和 SKHynix 合作,将该技术用于逻辑节点和 DRAM 节点的商业化。这显然很有希望。

面对汹涌袭来的新挑战者,东京电子和光刻胶老牌企业并没有坐以待毙, Inpria就是其中的代表。他们开发了一种新型光刻胶,金属氧化物抗蚀剂 (MOR)。

Inpria 于 2007 年诞生于俄勒冈州立大学研究中心。此后,Inpria 获得了来自三星、英特尔、应用材料、台积电、SKHynix、JSR 和 TOK 的大量投资。

Inpria 的投资者是该行业的巨头。它包括与 Lam Research 合作将干式抗蚀剂商业化的所有 4 家公司。该名单还包括前面提到的 CAR 光刻胶的领导者JSR 和TOK 。JSR 在 2017 年和 2020 年参与了 Inpria 的几轮融资,最近他们硬着头皮以 5.14 亿美元直接收购了该公司——对该公司的估值为 7.42 亿美元。对于一家以预收入为基础开发化学品的工业公司来说,这是一个令人印象深刻的估值。

很明显,该公司拥有价值不菲的知识产权。JSR 管理往往非常保守,因此它充分说明了正在发生的中断。光刻胶行业与 TokyoElectron 合作了数十年,而 JSR/Inpria 正在继续这种紧密结合的伙伴关系。他们正在共同开发光刻胶、工艺和涂布机/显影剂,以为下一个即将实现商业化工艺节点做好准备。

MOR 仍然使用与当前光刻工艺类似的步骤。通过悬浮在溶液中,将其旋涂到硅片上。他们可以通过升级,从而可以在相同的Tokyo Electron Clean Track Lithius Pro Z上使用。这种升级不是资本密集型的,且可以使用 CAR 或 MOR 光刻胶。

MOR 仍然是湿的,这意味着某些问题仍将存在,即沉积的选择性。晶圆上光刻胶的潜在不均匀沉积会导致曝光和烘烤工艺步骤出现问题。

Lam Research 干式抗蚀剂技术的最大优势之一是使用化学气相沉积 (CVD) 工艺来沉积光刻胶,从而可以更精细地控制光刻胶的可变性和厚度。

众所周知,获得合适的厚度对于光刻胶来说非常重要。如果有极薄的层,则光刻工具具有更高的性能和吞吐量,因为需要曝光的光刻胶更少。另一方面,蚀刻时会损坏薄抗蚀剂膜(负光致抗蚀剂)。厚的光刻胶层不仅会导致较低的吞吐量,还会导致图案塌陷和显影后残留的光刻胶留在孔中。

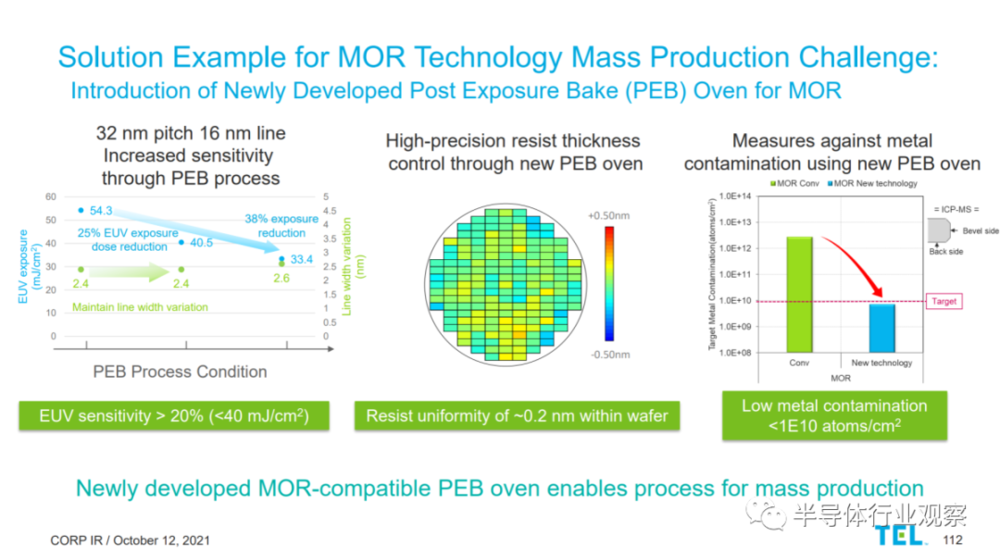

TokyoElectron 和 JSR 声称他们有一种新的金属氧化物抗蚀剂曝光后烘烤工艺,这将有助于提高光刻胶的灵敏度。这意味着晶圆厂可以显著降低 EUV 机器所需的剂量,从而提高产量。

TokyoElectron 声称用量减少了 38%,而 Lam Research 声称干式抗蚀剂用量减少了 50%。Tokyo Electron 还声称新的曝光后烘烤可实现极其均匀的抗蚀剂厚度和低金属污染。如果这些说法成立,那么这可以延长湿光刻胶的使用寿命。

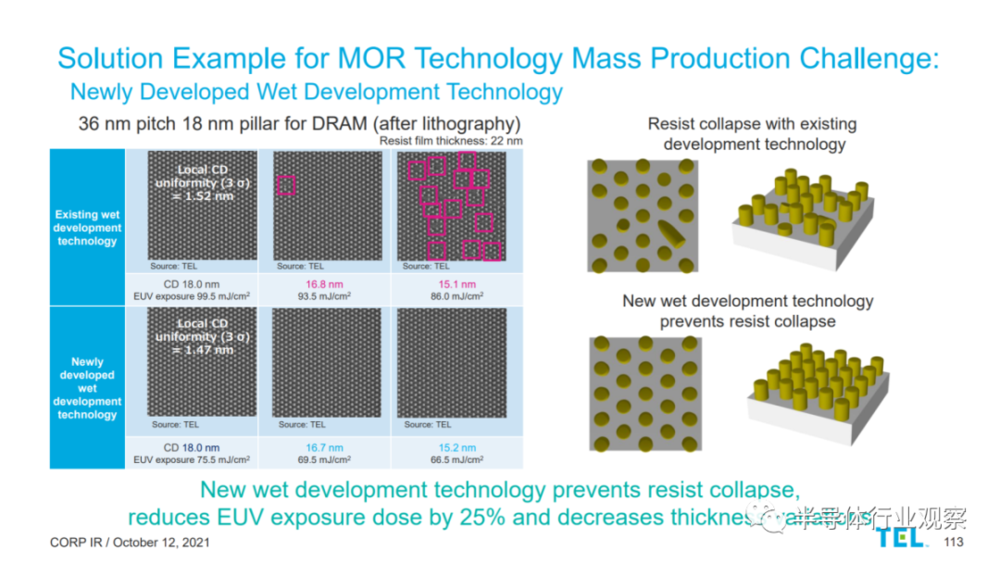

同样,Tokyo Electron 和 JSR 拥有新的湿法开发工艺,可以抵抗支柱倒塌(pillar collapse )问题。36nm 支柱经常崩塌,这是 DRAM 中电容器缩放的最大挑战之一。新的显影工艺也适用于较低的 EUV 剂量,并减少了最终特征的厚度变化。

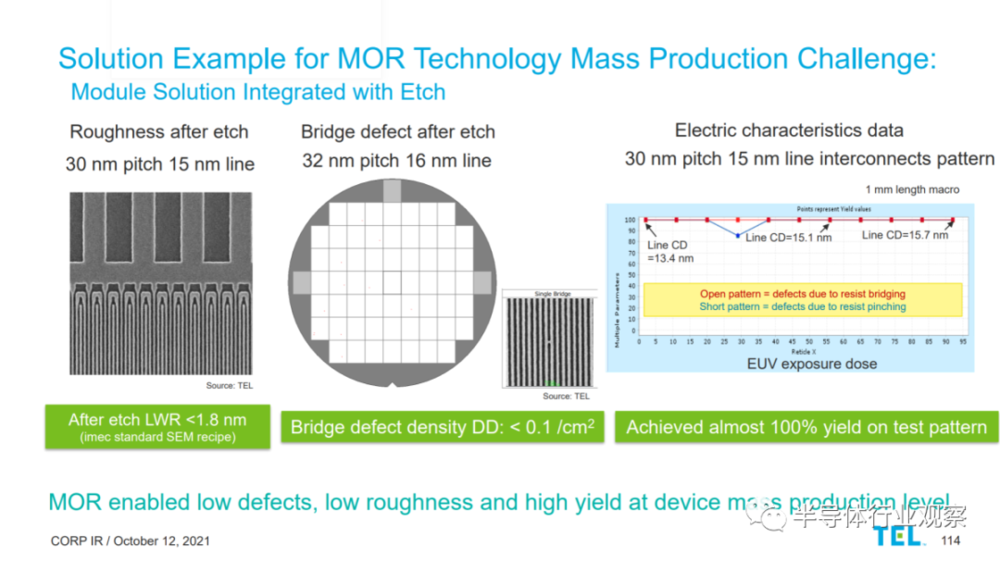

通过 MOR,Tokyo Electron 正在努力优化从涂层、烘烤、开发,并一直到蚀刻的整个工艺流程。他们声称他们已经实现了每平方厘米 0.1 个缺陷的缺陷密度。这听起来很棒,但这种缺陷密度意味着每 300 毫米晶圆有 70.6 个缺陷。光刻工艺在前沿晶圆上进行了 70 多次,而 N3 工艺将对每个晶圆进行 20 多次EUV 浸渍。那就意味着这些缺陷确实开始堆积并破坏产量。MOR 仍有一些障碍需要克服。

优化流程的想法并不是一个全新的想法。工艺模块优化是应用材料公司在其整个互连工艺流程和工具产品中已经做了很长时间的事情。由于东京电子在光刻胶涂布机/显影剂中的主导地位,它使东京电子在蚀刻和清洁领域获得了份额。Lam Research 同样希望通过提供从硬掩模到光刻胶沉积和开发一直到蚀刻的技术来渗透光刻市场。多步骤工艺优化允许最终用户芯片和工艺中的线边缘粗糙度更小、更均匀、缺陷更少以及更高的可靠性。

干法工艺显著降低了化学品的使用。这尤其适用于旋转抗蚀剂和显影。光刻胶不需要悬浮在溶液中进行沉积,也不会像湿法工艺那样产生废料。显影过程不需要用大量酸或超纯水冲洗硅片以溶解硅片上的光刻胶。这反过来又将所需的电量减半。

EUV光刻胶争夺,未来的输赢还有待观察,因为两种路线都都有好处,但毫无疑问,一场新的战斗已经打响。

本文来自微信公众号:半导体行业观察(ID:icbank),作者:Dylan Patel,编译自semianalysis