本文来自微信公众号:半导体行业观察(ID:icbank),作者:L晨光,题图来自:视觉中国

从1960年代到2010年代,缩小晶体管的工程创新大约每两年使单个计算机芯片上的晶体管数量增加一倍,摩尔定律引领了芯片速度和效率的持续提高。

10nm、7nm、5nm、3nm……这些逐渐缩小的芯片制程数字,正是全球电子产品整体性能不断进化的核心驱动力。随着制造更小的晶体管工程难度逐渐加剧,甚至无法解决,从而导致半导体行业的资本支出和人才成本以不可持续的速度增长。

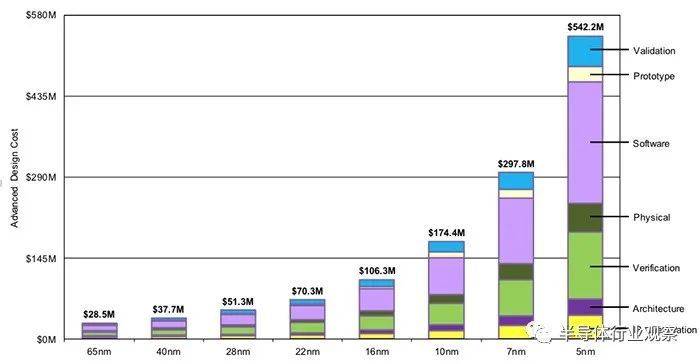

国际商业战略公司(IBS)首席执行官Handel Jones表示:“设计28nm芯片的平均成本为4000万美元。相比之下,设计7nm芯片的成本为2.17亿美元,设计5nm芯片设备的成本为 4.16亿美元,3nm芯片设计更是将耗资高达5.9亿美元。”

在先进工艺设计成本上,知名半导体技术研究机构Semiengingeering也统计了不同工艺下芯片所需费用,其中28nm节点上开发芯片只要5130万美元投入,16nm节点需要1亿美元,7nm节点需要2.97亿美元,到了5nm节点,开发芯片的费用将达到5.42亿美元,3nm节点的数据还没有,大概是因为3nm现在还在研发阶段,成本不好估算。但从这个趋势来看,3nm芯片研发费用或将接近10亿美元。

按照台积电、三星的说法,预计在2022年进入3nm阶段。可见,先进芯片的烧钱游戏正在加速。IBS数据显示,3nm工艺开发将耗资40亿至50亿美元,而兴建一条3nm产线的成本约为150亿~200亿美元。这一数据也解释了为什么台积电此前宣布的3nm晶圆厂需要200亿美元投资的原因。而三星为了进入3nm工艺,投的钱一点都不比台积电少,单从这一点来看,很多芯片制造企业就没有这个实力。

的确,制程工艺的研发和生产成本逐代上涨,飙高的技术难度和研发成本将大多数芯片代工厂拦在半山腰。2018 年,因高昂的研发成本,当时排名世界第二的代工厂格罗方德被迫放弃7nm制程的研发。目前,全球唯有台积电、三星、英特尔还在向峰顶冲刺。

在全球备战3nm及更先进制程工艺节点之际,本文围绕芯片设计和制造中的多个关键节点,来分析一下3nm芯片或先进制程芯片的成本究竟为何达到如此之高。

先进制程芯片成本为啥这么贵?

根据芯片的制造流程,可以分为主产业链和支撑产业链:主产业链包括芯片设计、制造和封测;支撑产业链包括IP、EDA、装备和材料等。其中,高昂的成本主要由人力与研发费用、流片费用、IP和EDA工具授权费等几部分组成。同时芯片制造环节涉及到的晶圆厂投资、晶圆制造以及相关设备成本也将会分摊到芯片整体成本之中。工艺制程越先进,成本更是随之提高。

晶圆代工成本

根据CEST的模型,在5nm节点上构建的单个300mm晶圆的成本约为16988美元,在7nm节点上构建的类似晶圆成本为9346美元。可以看到,相同尺寸晶圆,5nm工艺节点相比7nm每片晶圆代工售价高7000多美元。

从中可以推断出,在3nm节点上构建的晶圆成本或将达到3万美元左右,晶圆代工成本将进一步提高。

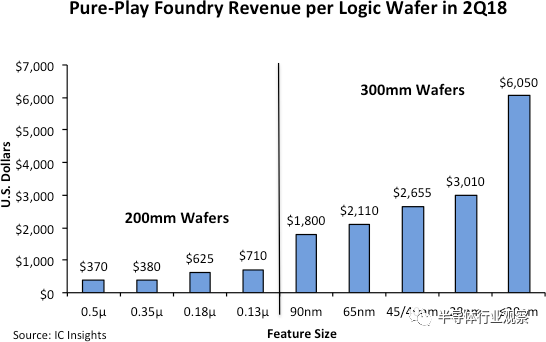

另一组数据也对此进行了印证,成本价格在很大程度上取决于芯片制程和晶圆尺寸的不同。IC Insights提供的数据显示,每片0.5µ 200mm晶圆代工收入(370美元)与≤20nm 300mm晶圆的代工收入(6050美元)之间相差超过16倍。即使同样是在300mm晶圆尺寸下,≤20nm 相比28nm工艺,成本相差也达到一倍。

可见,随着工艺节点的提升,晶圆代工成本随之大幅度提升。

此外,除了晶圆厂建设和代工费用,晶圆制造厂商的日常运营投入也不低(当然,此部分已经均摊到了代工成本里面)。

台积电企业社会责任报告书中的数据显示,2019年台积电全球能源消耗量达到143.3亿度,作为对比,2019年深圳市1343.88万常住人口的全年居民用电为146.64亿度。由此可见,台积电一年消耗的电量有多么巨大。

而且,精度越高的工艺,或精度越高的光刻设备,所需电量还会成正比增长。据台媒报道,以5nm为例,台积电5nm芯片大规模量产之际,公司单位产品用电量相比2019年上涨了17.9%。

掩膜(Mask)成本

掩膜版又称光罩、光掩膜等,是微电子制造过程中的图形转移工具或母版,其功能类似于传统照相机的“底片”,根据客户所需要的图形,通过光刻制版工艺,将微米级和纳米级的精细图案刻制于掩膜版基板上,是承载图形设计和工艺技术等内容的载体。

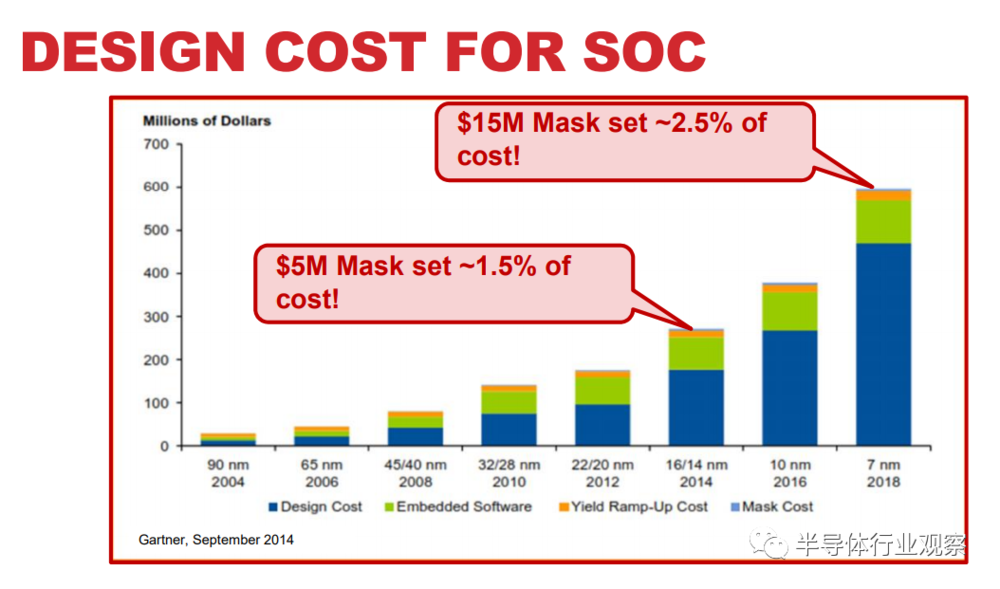

据IBS数据显示,在16/14nm制程中,所用掩膜成本在500万美元左右,到7nm制程时,掩膜成本迅速升至1500万美元。

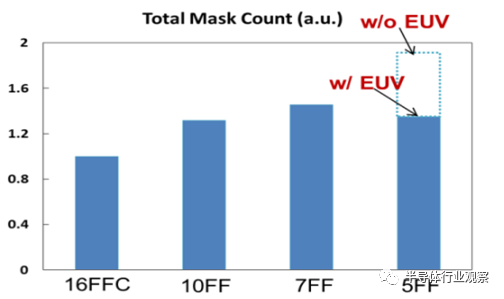

又从台积电(IEDM 2019)了解到,从10nm到5nm,随着EUV光刻技术的应用,掩膜使用数量有所减少,5nm与10nm制程中掩膜使用数量相差不多。

但是,在掩膜数量基本持平的情况下,更先进的制程工艺使得掩膜总成本提升,能侧面反映出掩膜平均成本在不断升高。

再反映到芯片成本上,每片CPU的掩膜成本等于掩膜总成本/总产量。如果总体产量小,芯片的成本会因为掩膜成本而较高;如果产量足够大,比如每年出货以亿计,掩膜成本被巨大的产量分摊,可以使每块CPU的掩膜成本大幅降低,使拥有“更贵的制程工艺+更大的产量”属性的CPU,比“便宜的制程工艺+较小的产量”的CPU成本更低。

可以预见,到3nm时,掩膜成本预计将会再度攀升,进一步增加芯片成本。

EUV光刻机

光刻机作为芯片制造阶段最核心的设备之一,负责“雕刻”电路图案,其精度决定了制程的精度,其原理是把设计好的芯片图案印在掩膜上,接着用激光光束穿过印着图案的掩膜和光学镜片,将芯片图案曝光在带有光刻胶涂层的硅片上,最终将掩膜上的图案转移到芯片光刻胶涂层上。

随着工艺制程的发展,到7nm及更先进的技术节点时,需要波长更短的极紫外(EUV)光刻技术来实现更小的制程。荷兰ASML是全球唯一有能力制造EUV光刻机的厂商。

台积电在7nm+时引入了EUV设备,但层数相对有限;6nm增加了EUV层并优化了PDK(工艺设计工具包);5nm具有完全EUV能力。随着芯片面向3nm及更先进的工艺,芯片制造商将需要一种高数值孔径EUV(high-NA EUV)的EUV光刻新技术。据ASML财报显示,他们正在研发采用high-NA技术的下一代EUV光刻机,有更高的数值孔径、分辨率和覆盖能力,较当前的EUV光刻机将提高70%。

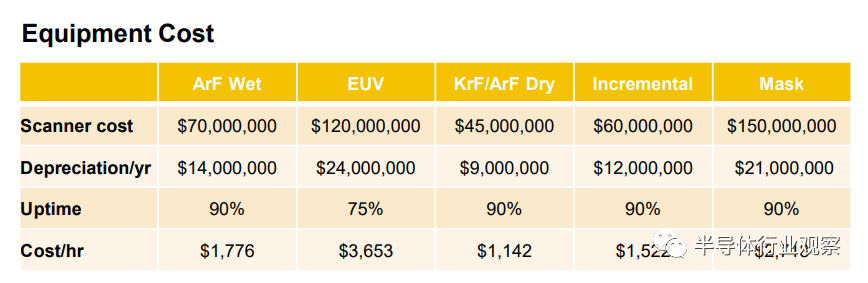

但EUV光刻机的价格一直以来十分昂贵,2018年,中芯国际和ASML签订了订购协议,以1.2亿美元的价格订购了一台EUV光刻机。这一价格与PHOTRONICS披露的EUV光刻机价格基本吻合。

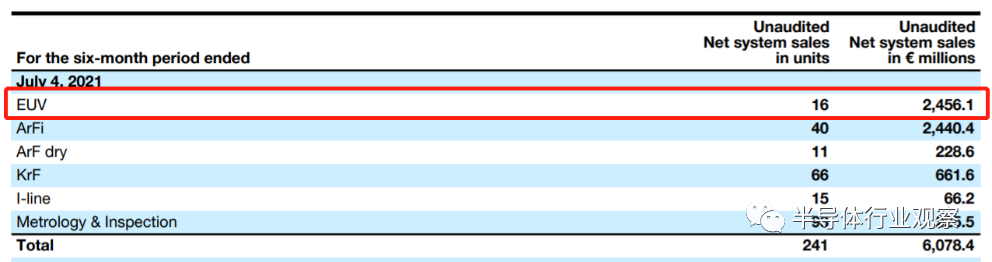

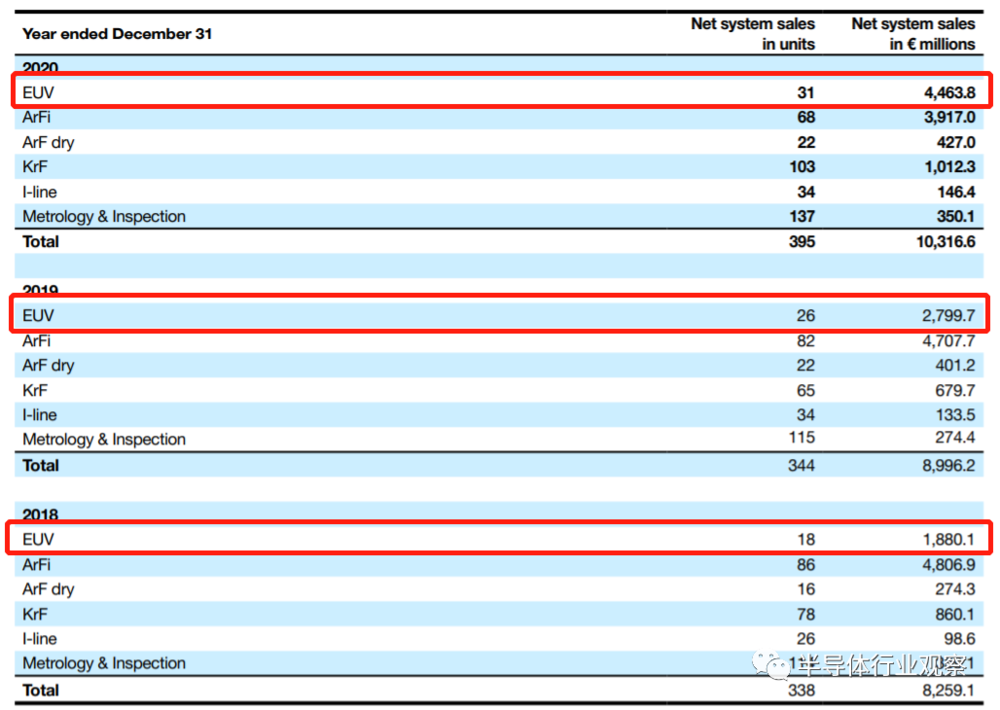

从ASML最新公布的2021年第二季度财报来看,截止2021年7月4日,ASML今年出货EUV光刻机16台,销售额达到24.561亿欧元,平均每台EUV光刻机价格高达1.535亿欧元。

再结合ASML历年(2018/2019/2020三年)财报数据,能够看到ASML的EUV光刻机单价从1.045亿欧元到1.44亿欧元,价格逐年攀升。

一台EUV光刻机售价超过1亿美元,而且还相当不好买。ASML每推出一代EUV光刻机,新设备的生产能力在稳步提升,但价格自然更高。据披露,ASML第二代EUV光刻机将会是NXE:5000系列,进一步提高光刻精度,原计划2023年问世,现推迟到2025~2026年,而价格预计将突破3亿美元。

当然,除了价格最贵的EUV光刻机之外,沉积、刻蚀、清洗、封装等环节所采用的设备和材料也价格不菲,且成本都在随着工艺制程向前发展不断提高。

研发&人力成本

先进制程不仅需要巨额的建设成本,高昂的研发和人力费用也提高了设计企业的门槛。

芯片设计包含电路设计、版图设计和光罩制作等,需要考虑多方面因素和知识结构。以大家较为熟悉的5G SoC为例,行业厂商能够集成自研的独立AI处理单元APU,多模通讯基带、相机ISP、各种控制开关、微核等多个自研模块。这部分成本很难具体估算,属于长期的研发成果,但投入力度从人力成本中可见一斑。

人力成本是研发成本的重要部分,项目开发效率和质量与工程师数量和水平相关,国内资深芯片设计工程师年薪一般在50-100万元之间。据了解,赛灵思在研发代号Everest的7nm工艺的FPGA芯片时提到,费时4年,动用了1500名工程师才开发成功,项目耗资超过10亿美元。FPGA芯片已经如此,更复杂的高端CPU、GPU芯片所需要的投资更是巨额数字,英伟达开发Xavier动用了2000个工程师,开发费用已达20亿美金。

芯片的开发成本取决于芯片尺寸、芯片类型等,有业内人士表示,最昂贵的设计(例如某些高端 CPU)比IBS提供的数据要高,但其他设计(例如某些ASIC)则要比IBS数据低得多。综合来看,随着芯片设计种类和形态千差万别,且正在不断发生变化,难以预测其具体成本。

另一方面,晶体管架构转向GAA,也在增加芯片成本。

当前随着深宽比不断拉高,FinFET逼近物理极限,为了制造出密度更高的芯片,环绕式栅极晶体管(GAAFET)成为新的技术选择。因此,晶体管结构从FinFET走向GAA,成为摩尔定律续命的关键。

三星、台积电、英特尔均引入GAA技术的研究,其中三星已经先一步将GAA用于3nm芯片设计。然而GAA当下还面临包括n/p不平衡、底部板的有效性、内部间隔、栅极长度控制和器件覆盖等在内的各种挑战。

在科技变革的过程中,新的技术需要更多时间来开发,在各环节需要新的技术和设备,这一切都在加大芯片开发的成本。

EDA成本

EDA涵盖了集成电路设计、验证和仿真等所有流程,芯片的用途、规格、特性、制成工艺几乎全都在这个阶段完成。利用EDA工具可设计得到极其复杂的电路图,从而制造出功能强大的芯片。

根据ESD Alliance数据显示,2020年EDA全球市场规模114.67亿美元,相对于几千亿美元的芯片市场来说占比较小,但EDA对芯片设计的效率和成本都起着至关重要的作用。

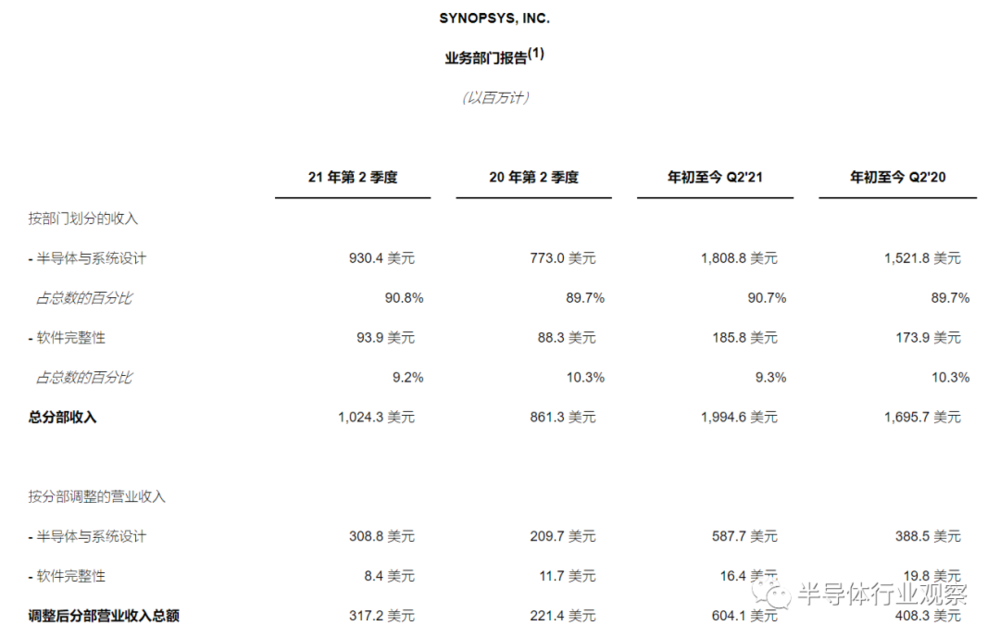

EDA是一个市场规模虽然小但技术流程很长的产业,需要种类繁多的软硬件工具相互配合从而形成工具链,以EDA巨头Synopsys为例,其完整覆盖芯片全设计流程的工具链号称有500多种。从Synopsys和Cadence的财报来看,2020年营收分别为36.9、26.8亿美元,两家公司每年花费在研发上的投入达到35%以上,Synopsys的研发费用更是达到惊人的十亿美金级别,EDA 软件的研发成本正在加速提升。

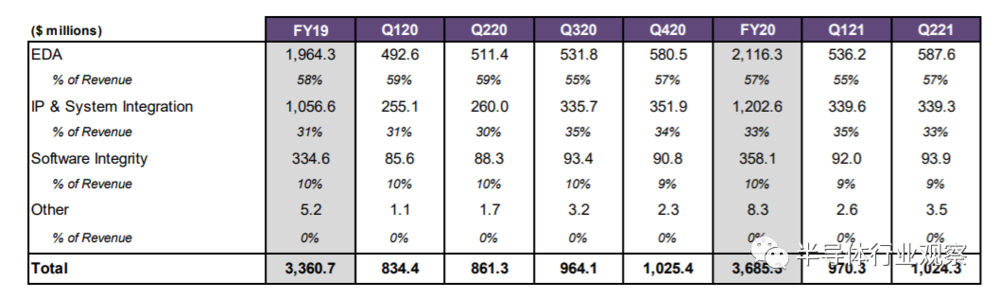

根据Synopsys 最新财报来数据,2021年第二季度营收10.243亿美元,半导体和系统设计,包括EDA工具、IP产品、系统集成解决方案和相关服务;软件完整性,包括用于软件开发的安全和质量解决方案等。EDA营收达到5.876亿美元,占比在57%左右。

据网上数据,20人的研发团队设计一款芯片所需要的EDA工具采购费用在100万美元/年(包括EDA和LPDDR等IP购买成本)。从EDA的行业属性及高昂的研发投入能够预测,待到3nm制程时,EDA工具授权费自然更是不菲。

IP授权成本

半导体IP是指在集成电路设计中那些已验证、可复用、具有某种确定功能和自主知识产权功能的设计模块,芯片公司可以通过购买IP实现某个特定功能(例如ARM的Cortex系列CPU、Mali系列GPU IP授权等,其他小的模块也要购买,如音视频编解码器、DSP、NPU等),这种类似“搭积木”的开发模式可大大缩短芯片的开发周期,在降低芯片设计难度的同时提高性能和可靠性。

芯片设计主要由于芯片核心的底层架构(知识产权和技术壁垒)被掌握在少数厂商手中,专利费可能达到设计成本的50%以上。据了解,ARM在过去通常要求客户选择一种特定的芯片设计方案,并预先为其支付授权许可费。这种模式一般都需要厂商一次性花费数百万美元才能被允许使用(具体金额取决于所授权技术的复杂程度,通常在100万美元到1000万美元之间),同时在芯片投产之后再以芯片最终售价的1%~3%向IP厂商支付版税。

另一方面,根据Synopsys和Cadence业绩数据,Synopsys公司IP和系统集成部份营收占比从2017年的28%提升至2020年的33%,达到1202.6万美元;Cadence公司IP部分占比从2016年的11%提升至2020年的 14%。

可见,IP作为技术含量最高的价值节点,随着芯片制程越来越先进,芯片价格的提升,IP研发难度和授权费用也将随之升高。

写在最后

上述种种因素和环节叠加之下,先进制程的芯片成本自然是居高不下。

笔者做不到对3nm或任何工艺节点的成本价格进行精确推算和预测,只是在能够搜集到有限的数据基础上得出尽可能客观的观点。同时希望大家能够基于此,更好的理解先进工艺对芯片成本带来巨大提升的原因所在。

当前,随着半导体制程的不断发展,摩尔定律的推进节奏逐渐趋缓,芯片成本问题成为阻碍先进制程发展的重要因素,但成本又绝不会是其根本原因。说到底,钱终归只是辅助作用。

FinFET技术发明人胡正明教授曾说过,半导体行业大约每隔20年就会有新的危机出现。20年前,大家一度非常悲观,看不清如何才能将芯片性能做得更好、功耗更低且控制住成本。

如今,半导体行业或是又来到了20年周期的危机循环节点,延续摩尔定律的生命力需要的是创新技术和设备的突破。当先进制程走到3nm、2nm、1nm后,未来半导体行业的发展,路又在何方?

本文来自微信公众号:半导体行业观察(ID:icbank),作者:L晨光